OpenSPARC T2

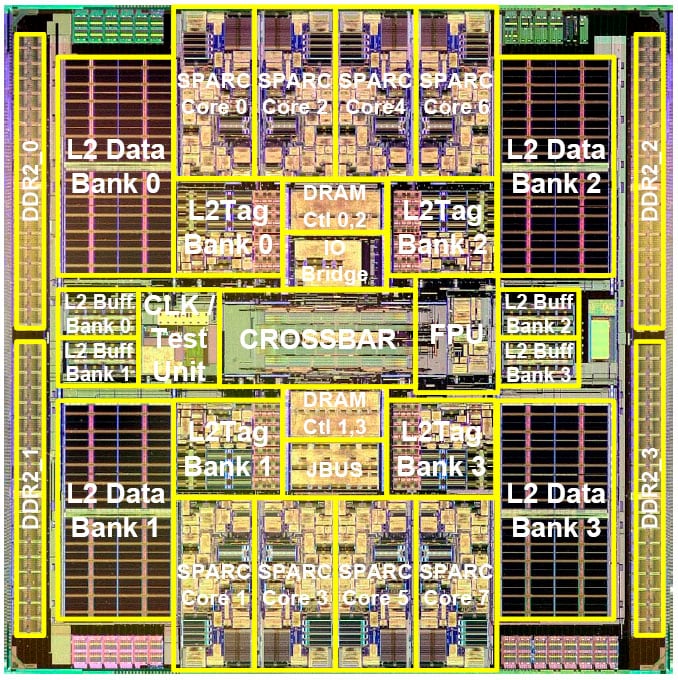

OpenSPARC T2 is derived from the UltraSPARC T2 processor, a 64 bit eight core multi-threaded microprocessor. The UltraSPARC T2 processor is industry's first "server on a chip", packaging the most cores and threads of any general-purpose processor available, and integrating all the key functions of a server on a single chip: computing, networking, security, and input/output (I/O), plus tight integration with the Solaris operating system.

By making the source for this design available for a larger community to review and learn from, we expect that ideas around chip multi-threading and multi-core concepts can be explored more freely and openly, and that truly beneficial innovations can be achieved.

OpenSPARC T2 source components are covered under multiple open source licenses. The majority of OpenSPARC T2 source code is released under the GNU General Public License. Source based on existing open source projects will continue to be available under their current licenses. Binary programs are released under a binary Software License Agreement.

Ultra SPARC T2 Technology: A Second Life Video Fly-Over

OpenSPARC T2 Documents and Specifications

- OpenSPARC T2 Implementation Supplement, Hyperprivileged Edition (608 pages)

(a.k.a. OpenSPARC T2 Programmer's Reference Manual)

This document contains information about processor-specific aspects of the architecture and programming of the OpenSPARC T2 processor. It is intended to supplement the UltraSPARC Architecture 2007 Specification with processor-specific information.

- OpenSPARC T2 Core Microarchitecture Specification (296 pages)

This OpenSPARC T2 Core Microarchitecture Specification includes detailed functional descriptions of the OpenSPARC T2 SPARC core processor components. This manual also provides I/O signal list for each component. This processor expands Sun's throughput computing initiative by doubling the number of threads from the OpenSPARC T1 processor.

- OpenSPARC T2 System-On-Chip (SoC) Microarchitecture Specification Vol. 1 (527 pages)

OpenSPARC T2 System-On-Chip (SoC) Microarchitecture Specification Vol. 2 (602 pages)

This OpenSPARC T2 System-On-Chip (SoC) Microarchitecture Specification includes detailed functional descriptions of the OpenSPARC T2 System-on-Chip I/O components. This manual also provides I/O signal list for each component. This processor expands Sun's throughput computing initiative by doubling the number of threads from the OpenSPARC T1 processor and adding support for industry standard I/O interfaces like 10Gigabit Ethernet.

- OpenSPARC T2 Processor Design and Verification User's Guide (68 pages)

The OpenSPARC T2 Processor Design and Verification User's Guide gives an overview of the design hierarchy on the OpenSPARC T2 processor. It also describes the files, procedures, and tools needed for running simulations and synthesis on the OpenSPARC T2 processor.

- OpenSPARC T2 Processor Megacell Specification (225 pages)

This document provides information regarding the megacells used in the OpenSPARC T2 processor, which is the first chip multiprocessor that fully implements the Sun Throughput Computing Initiative.

UltraSPARC Architecture 2007 Documents

- UltraSPARC Architecture 2007 Specification, Hyperprivileged Edition (768 pages)

UltraSPARC Architecture 2007 Specification, Privileged Edition (578 pages)(a.k.a. UA 2007 Family Programmer's Reference Manual)

The UltraSPARC Architecture 2007 is a complete specification of the instruction set architecture (ISA) common to Sun Microsystem's 64-bit SPARC implementations (beginning with UltraSPARC T1 in 2005). UltraSPARC Architecture 2007 complies with SPARC V9 Level 1, with many more details, plus includes numerous Sun extensions common to all UltraSPARC processors. Information in this (and the following) documents can help with Operating Systems ports (including Linux).

The Privileged edition of this document describes the full Nonprivileged (application software) and Privileged (operating system software) levels of the architecture. Download it if you are writing application software, writing a code generator, or writing/porting operating system software to run on top of existing Hypervisor firmware.

The Hyperprivileged edition of this document describes the Nonprivileged, Privileged, and Hyperprivileged (hypervisor/virtual machine firmware) levels of the architecture. Download it if you are writing hyperprivileged firmware ("Hypervisor" code) or designing your own processor based on OpenSPARC.

UltraSPARC T2 Programmer's Reference Model

- UltraSPARC T2 Implementation Supplement, Privileged Edition (146 pages)

UltraSPARC T2 Implementation Supplement, Hyperprivileged Edition (1184 pages)(a.k.a. UltraSPARC T2 Programmer's Reference Manual)

This document contains information about processor-specific aspects of the architecture and programming of the UltraSPARC T2 processor. It is intended to supplement the UltraSPARC Architecture 2007 Specification with processor-specific information.

T2 Processor Tips and Downloads

Here's tips to download one or both the OpenSPARC T2 "Chip Design and Verification" and the "OpenSPARC T2 Architecture and Performance Modelings" software tools.

- Step 1: Download one or both of the following files and then use bunzip2 command to create OpenSPARCT2.x.x.tar file. e.g. bunzip2 OpenSPARCT2.1.1.tar.bz2

OpenSPARC T2 Chip Design and Verification download

OpenSPARCT2.1.3.tar.bz2 (bzip2 compression, 278,662,085 bytes)

OpenSPARC T2 Architecture and Performance Modeling download

OpenSPARCT2_Arch.1.2.tar.bz2 (bzip2 compression, 373,795,542bytes)

- Step 2:

Use the following command to extract files from tar file : tar xvf OpenSPARCT2.x.x.tar

- Step 3:

For the Chip Design and Verification download, please follow the instructions in the README file in the download to run simulations or synthesis. Also refer to Design/Verification Users Guide document included in the download.

For the Architecture and Performance Modeling download, please follow the instructions in the README file in the download to setup and run SAM.

For hardware design and verification engineers, the download includes:

- Verilog RTL for OpenSPARC T2 design

- Verification environment for OpenSPARC T2

- Diagnostics tests for OpenSPARC T2

- Scripts and Sun internal tools needed to simulate the design and to do synthesis of the design

- Open source tools needed to simulate the design

System Requirements:

- SPARC CPU based system with Solaris 9 or Solaris 10 Operating System

- C/C++ Compiler, if you don't have it download Sun Studio 12.

Commercial EDA tools Requirements:

- Verilog Simulator : Synopsys VCS©

- Synthesis : Synopsys Design Compiler©

OpenSPARC T2 Processor Download for Architecture and Performance Modeling Tools

SAM (SPARC Architectural Model) is a full system simulator that is able to boot hypervisor, OBP (Open Boot PROM) and Solaris and run applications. It loads SAS (SPARC Architecture Simulator) as the OpenSPARC T2 simulator. So any modifications made in SAS get automatically reflected in SAM. SAM is useful for software bring up work -- for instance to debug Hypervisor/OBP/Solaris on a modified CPU implementation. SAM is also useful for performance analysis, both to generate traces and to connect with a performance model to perform execution driven simulation. SAM loads device models as dynamically linked libraries, and is useful for device driver development, and device RTL verification.

Legion is a fast instruction accurate simulator which provides a rapid means of developing and testing software functionality in the absence of actual hardware. Legion provides the fastest simulation environment for developing and testing SPARC Software. Firmware and Software developers will be the primary users of Legion simulation environment for the OpenSPARC T2.

OpenSPARC T2 source components are covered under multiple open source licenses. The majority of OpenSPARC T2 source code is released under the GNU General Public License. Source based on existing open source projects will continue to be available under their current licenses. Binary programs are released under a binary Software License Agreement.

This download area is for software engineers and architects, it includes;

- SAM - SPARC Architecture Model (including source code)

- Legion - Fast instruction accurate simulator for software developers (including source code)

- SAM/Legion enhancements to copy files to/from simulated disk

- SAS - Instruction accurate SPARC Architecture Simulator (including source code)

- OBP - Open Boot PROM source code

- Hypervisor source code

- Solaris Images for simulation

- RST Trace Tool - RST is a trace format for SPARC instruction-level traces. The RST Tools package consists of the trace format definition, a trace reader/writer library, and a trace viewer program.

System Requirements:

- SPARC CPU based system with Solaris 9 or Solaris 10 Operating System

- C/C++ Compiler, if you don't have it download Sun Studio 12 .