# UltraSPARC Architecture 2007

# *One Architecture ... Multiple Innovative Implementations*

Draft D0.9.4, 27 Sep 2010

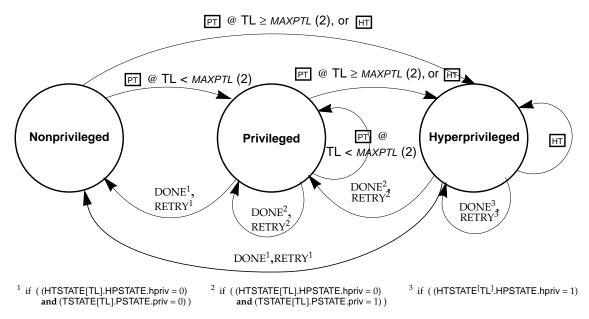

Privilege Levels: Hyperprivileged, Privileged, and Nonprivileged

Distribution:

Public

Part No: 950-5554-15 Revision: Draft D0.9.4, 27 Sep 2010

> Oracle Corporation 4150 Network Circle Santa Clara, CA 95054 U.S.A. 650-960-1300

Copyright © 2007, 2011, Oracle and/or its affiliates. All rights reserved.

Oracle and Java are registered trademarks of Oracle and/or its affiliates. Other names may be trademarks of their respective owners.

AMD, Opteron, the AMD logo, and the AMD Opteron logo are trademarks or registered trademarks of Advanced Micro Devices. Intel and Intel Xeon are trademarks or registered trademarks of Intel Corporation. All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. UNIX is a registered trademark licensed through X/Open Company, Ltd..

Comments and "bug reports" regarding this document are welcome; they should be submitted to email address: UA-editor@sun.com

# Contents

|   | Pref              | ace                                            | •••••                                                                                                    | i                                                                                                                                                                                                                                                                                                                   |

|---|-------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | Doc               | ument Ove                                      | erview                                                                                                   |                                                                                                                                                                                                                                                                                                                     |

|   | 1.1<br>1.2<br>1.3 | Fonts and<br>1.2.1<br>1.2.2<br>1.2.3           | l Notationa<br>Implem<br>Notatio<br>Informa                                                              | ARC Architecture 20071Il Conventions2centation Dependencies3n for Numbers3ational Notes3this Specification4                                                                                                                                                                                                         |

| 2 | Defi              | nitions                                        |                                                                                                          |                                                                                                                                                                                                                                                                                                                     |

| 3 | Arch              | itecture O                                     | verview                                                                                                  |                                                                                                                                                                                                                                                                                                                     |

|   | 3.1               | The Ultra<br>3.1.1<br>3.1.2                    | Feature<br>Attribu<br>3.1.2.1                                                                            | chitecture 2007                                                                                                                                                                                                                                                                                                     |

|   |                   | 3.1.3                                          | 3.1.2.2<br>System<br>3.1.3.1<br>3.1.3.2<br>3.1.3.3                                                       | Register Windows17Components17Binary Compatibility17UltraSPARC Architecture 2007 MMU17Privileged Software17                                                                                                                                                                                                         |

|   |                   | 3.1.4<br>3.1.5<br>3.1.6                        | Archite<br>UltraSP                                                                                       | ctural Definition                                                                                                                                                                                                                                                                                                   |

|   | 3.2               | Processon<br>3.2.1<br>3.2.2                    | Integer                                                                                                  | ıre                                                                                                                                                                                                                                                                                                                 |

|   | 3.3               | Instructic<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4 | Memor<br>3.3.1.1<br>3.3.1.2<br>3.3.1.3<br>3.3.1.4<br>3.3.1.5<br>3.3.1.6<br>3.3.1.7<br>Integer<br>Control | 19y Access19Memory Alignment Restrictions20Addressing Conventions20Addressing Range20Load/Store Alternate20Separate Instruction and Data Memories21Input/Output (I/O)21Memory Synchronization21Arithmetic / Logical / Shift Instructions21Transfer22egister Access22Ancillary State Registers22PR State Registers22 |

| 3.3.5       Floating-Point Operate.       22         3.3.6       Conditional Move       22         3.3.7       Register Window Management.       22         3.3.8       SIMD.       22         3.4       Traps       22         3.5       Chip-Level Multithreading (CMT)       24         4       Data Formats       22         4.1       Integer Data Formats       24         4.1.1       Signed Integer Data Types       24         4.1.1       Signed Integer Data Types       24         4.1.1.2       Signed Integer Data Types       24         4.1.1.2       Signed Integer Data Types       22         4.1.1.2       Unsigned Integer Data Types       22         4.1.2       Unsigned Integer Data Types       22                                                                                                                                                                    |           | 0                    | -Point Operate                               | 22 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------|----------------------------------------------|----|

| 3.3.7       Register Window Management.       22         3.3.8       SIMD.       22         3.4       Traps.       22         3.5       Chip-Level Multithreading (CMT)       24         4       Data Formats.       22         4.1       Integer Data Formats       24         4.1.1       Signed Integer Data Types.       26         4.1.1       Signed Integer Data Types.       26         4.1.1.2       Signed Integer Doubleword (64 bits)       27         4.1.2       Unsigned Integer Data Types.       27         4.1.2       Unsigned Integer Data Types       27         4.1.2       Unsigned Integer Doubleword (64 bits)       22         4.1.2.1       Unsigned Extended Integer (64 bits)       22         4.1.3       Tagged Word (32 bits)       22         4.2       Floating-Point Data Formats       22         4.2.1       Floating Point, Double Precision (32 bits)       23         4.2.3       Floating Point, Double Precision (64 bits)       24         4.2.4                                                                                                                                         |           | 3.3.6 Condition      |                                              |    |

| 3.3.8       SIMD.       22         3.4       Traps.       22         3.5       Chip-Level Multithreading (CMT)       24         4       Data Formats.       26         4.1       Integer Data Formats       26         4.1.1       Signed Integer Data Types.       26         4.1.1       Signed Integer Data Types.       26         4.1.1       Signed Integer Byte, Halfword, and Word.       27         4.1.1.2       Signed Integer Doubleword (64 bits)       27         4.1.2       Unsigned Integer Data Types.       27         4.1.2       Unsigned Integer Data Types       27         4.1.2       Unsigned Integer Data Types       27         4.1.2       Unsigned Integer Doubleword (64 bits)       28         4.1.2       Unsigned Integer Doubleword (64 bits)       28         4.1.2       Unsigned Integer Doubleword (64 bits)       28         4.1.2.1       Unsigned Extended Integer (64 bits)       28         4.1.3       Tagged Word (32 bits)       28         4.2       Floating Point, Double Precision (32 bits)       29         4.2.1       Floating Point, Double Precision (64 bits)       29         4.2.2       Floating Point Quad Precision (128 bits)       33 <td></td> <td></td> <td></td> <td></td>                                                                 |           |                      |                                              |    |

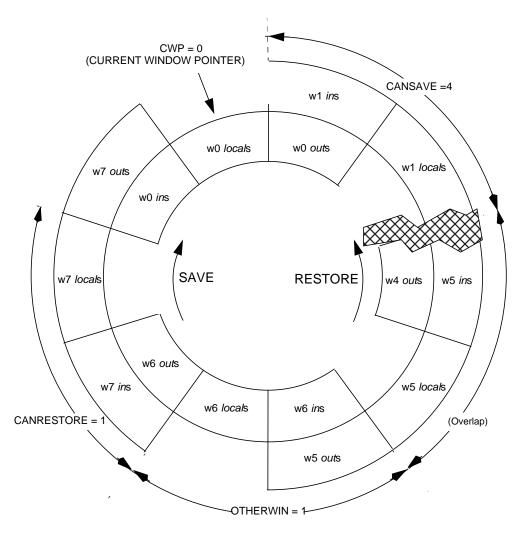

| 3.4       Traps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           | 3.3.7 Register       | Window Management.                           | 23 |

| 3.5       Chip-Level Multithreading (CMT)       24         4       Data Formats       23         4.1       Integer Data Formats       26         4.1.1       Signed Integer Data Types       26         4.1.1       Signed Integer Data Types       26         4.1.1       Signed Integer Data Types       26         4.1.1       Signed Integer Byte, Halfword, and Word       27         4.1.2       Signed Integer Extended-Word (64 bits)       27         4.1.2       Unsigned Integer Data Types       27         4.1.2       Unsigned Integer Doubleword (64 bits)       27         4.1.2       Unsigned Integer Byte, Halfword, and Word       28         4.1.2       Unsigned Integer Doubleword (64 bits)       28         4.1.2       Unsigned Integer Doubleword (64 bits)       28         4.1.3       Tagged Word (32 bits)       28         4.1.3       Tagged Word (32 bits)       28         4.2       Floating-Point Data Formats       29         4.2.1       Floating Point, Single Precision (32 bits)       29         4.2.2       Floating Point, Quad Precision (128 bits)       30         4.2.3       Floating-Point Data Alignment in Memory and Registers       33         4.3       I                                                                                             |           |                      |                                              |    |

| 4 Data Formats.       24         4.1 Integer Data Formats       26         4.1.1 Signed Integer Data Types.       26         4.1.1 Signed Integer Data Types.       26         4.1.1 Signed Integer Data Types.       26         4.1.1 Signed Integer Doubleword (64 bits)       27         4.1.1.2 Signed Integer Doubleword (64 bits)       27         4.1.2 Unsigned Integer Extended-Word (64 bits)       27         4.1.2 Unsigned Integer Doubleword (64 bits)       27         4.1.2.1 Unsigned Integer Doubleword (64 bits)       28         4.1.2.2 Unsigned Integer Doubleword (64 bits)       28         4.1.2.3 Unsigned Extended Integer (64 bits)       28         4.1.3 Tagged Word (32 bits)       28         4.2 Floating-Point Data Formats       29         4.2.1 Floating Point, Single Precision (32 bits)       29         4.2.2 Floating Point, Double Precision (64 bits)       29         4.2.3 Floating Point, Quad Precision (128 bits)       30         4.3.1 Uint8 SIMD Data Formats       31         4.3.2 Int16 SIMD Data Formats       32         4.3.3 Int32 SIMD Data Formats       32         4.3.3 Int32 SIMD Data Formats       32         5.1 Reserved Register Fields       34         5.2 General-Purpose R Registers       35 <th></th> <th></th> <th></th> <th></th> |           |                      |                                              |    |

| 4.1       Integer Data Formats       26         4.1.1       Signed Integer Data Types       26         4.1.1       Signed Integer Data Types       26         4.1.1.1       Signed Integer Byte, Halfword, and Word       27         4.1.1.2       Signed Integer Doubleword (64 bits)       27         4.1.1.3       Signed Integer Extended-Word (64 bits)       27         4.1.2       Unsigned Integer Data Types       27         4.1.2.1       Unsigned Integer Byte, Halfword, and Word       28         4.1.2.1       Unsigned Integer Doubleword (64 bits)       28         4.1.2.2       Unsigned Integer Doubleword (64 bits)       28         4.1.2.3       Unsigned Extended Integer (64 bits)       28         4.1.3       Tagged Word (32 bits)       29         4.1.3       Tagged Word (32 bits)       29         4.2       Floating-Point Data Formats       29         4.2.1       Floating Point, Single Precision (32 bits)       29         4.2.1       Floating Point, Quad Precision (128 bits)       30         4.2.4       Floating-Point Data Alignment in Memory and Registers       31         4.3       SIMD Data Formats       31         4.3.1       Uint8 SIMD Data Format       32 <t< th=""><th>3.5 C</th><th>hip-Level Multithre</th><th>eading (CMT)</th><th>24</th></t<> | 3.5 C     | hip-Level Multithre  | eading (CMT)                                 | 24 |

| 4.1.1Signed Integer Data Types264.1.1.1Signed Integer Byte, Halfword, and Word274.1.1.2Signed Integer Doubleword (64 bits)274.1.1.3Signed Integer Data Types274.1.2Unsigned Integer Data Types274.1.2Unsigned Integer Data Types274.1.2.1Unsigned Integer Byte, Halfword, and Word284.1.2.2Unsigned Integer Doubleword (64 bits)284.1.2.3Unsigned Integer Doubleword (64 bits)284.1.3Tagged Word (32 bits)284.1.3Tagged Word (32 bits)284.2Floating-Point Data Formats294.2.1Floating Point, Single Precision (32 bits)294.2.2Floating Point, Double Precision (64 bits)294.2.3Floating Point, Quad Precision (128 bits)304.2.4Floating-Point Data Alignment in Memory and Registers334.3Int16 SIMD Data Formats324.3.3Int32 SIMD Data Formats324.3.3Int32 SIMD Data Format325.1Reserved Register Fields345.2General-Purpose R Registers35                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |                      |                                              |    |

| 4.1.1.1Signed Integer Byte, Halfword, and Word.274.1.1.2Signed Integer Doubleword (64 bits)274.1.1.3Signed Integer Extended-Word (64 bits)274.1.2Unsigned Integer Data Types274.1.2.1Unsigned Integer Data Types274.1.2.2Unsigned Integer Byte, Halfword, and Word284.1.2.3Unsigned Integer Doubleword (64 bits)284.1.2.4Unsigned Integer Doubleword (64 bits)284.1.3Tagged Word (32 bits)284.1.3Tagged Word (32 bits)294.2Floating-Point Data Formats294.2.1Floating Point, Single Precision (32 bits)294.2.2Floating Point, Double Precision (64 bits)294.2.3Floating Point, Quad Precision (128 bits)304.2.4Floating-Point Data Alignment in Memory and Registers334.3SIMD Data Formats324.3.1Uint8 SIMD Data Formats324.3.2Int16 SIMD Data Formats324.3.3Int32 SIMD Data Format325.1Reserved Register Fields345.2General-Purpose R Registers35                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4.1 In    | teger Data Formats   | 3                                            | 26 |

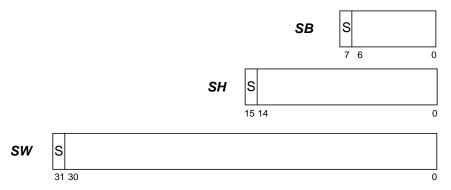

| 4.1.1.1Signed Integer Byte, Halfword, and Word.274.1.1.2Signed Integer Doubleword (64 bits)274.1.1.3Signed Integer Extended-Word (64 bits)274.1.2Unsigned Integer Data Types274.1.2.1Unsigned Integer Data Types274.1.2.2Unsigned Integer Byte, Halfword, and Word284.1.2.3Unsigned Integer Doubleword (64 bits)284.1.2.4Unsigned Integer Doubleword (64 bits)284.1.3Tagged Word (32 bits)284.1.3Tagged Word (32 bits)294.2Floating-Point Data Formats294.2.1Floating Point, Single Precision (32 bits)294.2.2Floating Point, Double Precision (64 bits)294.2.3Floating Point, Quad Precision (128 bits)304.2.4Floating-Point Data Alignment in Memory and Registers334.3SIMD Data Formats324.3.1Uint8 SIMD Data Formats324.3.3Int32 SIMD Data Formats325.1Reserved Register Fields345.2General-Purpose R Registers35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           | 4.1.1 Signed I       | nteger Data Types                            | 26 |

| 4.1.1.3       Signed Integer Extended-Word (64 bits)       27         4.1.2       Unsigned Integer Data Types       27         4.1.2       Unsigned Integer Data Types       27         4.1.2.1       Unsigned Integer Byte, Halfword, and Word       28         4.1.2.2       Unsigned Integer Doubleword (64 bits)       28         4.1.2.3       Unsigned Extended Integer (64 bits)       28         4.1.3       Tagged Word (32 bits)       28         4.1.3       Tagged Word (32 bits)       29         4.1.3       Tagged Word (32 bits)       29         4.2       Floating-Point Data Formats       29         4.2.1       Floating Point, Single Precision (32 bits)       29         4.2.2       Floating Point, Double Precision (64 bits)       29         4.2.3       Floating-Point Data Alignment in Memory and Registers       30         4.3       SIMD Data Formats       31         4.3.1       Uint8 SIMD Data Formats       32         4.3.2       Int16 SIMD Data Formats       32         4.3.3       Int32 SIMD Data Format       33         5.1       Reserved Register Fields       34         5.2       General-Purpose R Registers       35                                                                                                                                      |           |                      |                                              |    |

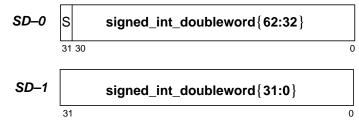

| 4.1.2Unsigned Integer Data Types274.1.2.1Unsigned Integer Byte, Halfword, and Word284.1.2.2Unsigned Integer Doubleword (64 bits)284.1.2.3Unsigned Extended Integer (64 bits)284.1.3Tagged Word (32 bits)284.2Floating-Point Data Formats294.2.1Floating Point, Single Precision (32 bits)294.2.2Floating Point, Double Precision (64 bits)294.2.3Floating Point, Double Precision (64 bits)294.2.4Floating-Point Data Alignment in Memory and Registers334.3SIMD Data Formats334.3.1Uint8 SIMD Data Formats334.3.3Int32 SIMD Data Format335Registers335.1Reserved Register Fields345.2General-Purpose R Registers35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           | 4.1.1.2              | Signed Integer Doubleword (64 bits)          | 27 |

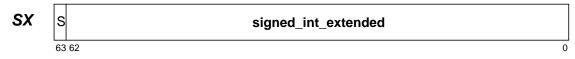

| 4.1.2.1Unsigned Integer Byte, Halfword, and Word244.1.2.2Unsigned Integer Doubleword (64 bits)244.1.2.3Unsigned Extended Integer (64 bits)284.1.3Tagged Word (32 bits)284.2Floating-Point Data Formats294.2.1Floating Point, Single Precision (32 bits)294.2.2Floating Point, Double Precision (64 bits)294.2.3Floating Point, Double Precision (64 bits)294.2.4Floating-Point Data Alignment in Memory and Registers334.3SIMD Data Formats334.3.1Uint8 SIMD Data Formats334.3.3Int16 SIMD Data Format335Registers335.1Reserved Register Fields345.2General-Purpose R Registers35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           | 4.1.1.3              | Signed Integer Extended-Word (64 bits)       | 27 |

| 4.1.2.2       Unsigned Integer Doubleword (64 bits).       24         4.1.2.3       Unsigned Extended Integer (64 bits)       26         4.1.3       Tagged Word (32 bits).       26         4.1.3       Tagged Word (32 bits).       26         4.1.4       Floating-Point Data Formats       26         4.2       Floating-Point Data Formats       29         4.2.1       Floating Point, Single Precision (32 bits)       29         4.2.2       Floating Point, Double Precision (64 bits)       29         4.2.3       Floating Point, Quad Precision (128 bits)       30         4.2.4       Floating-Point Data Alignment in Memory and Registers       31         4.3       SIMD Data Formats       31         4.3.1       Uint8 SIMD Data Formats       32         4.3.2       Int16 SIMD Data Formats       32         4.3.3       Int32 SIMD Data Formats       32         5.1       Reserved Register Fields       34         5.2       General-Purpose R Registers       33                                                                                                                                                                                                                                                                                                                      |           | 4.1.2 Unsigne        | d Integer Data Types                         | 27 |

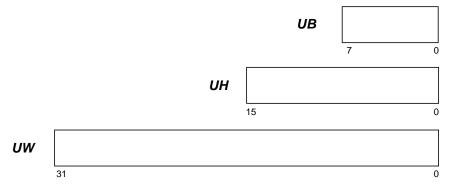

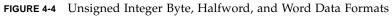

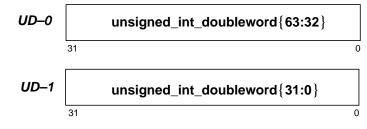

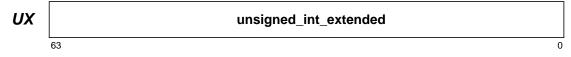

| 4.1.2.3       Unsigned Extended Integer (64 bits)       24         4.1.3       Tagged Word (32 bits)       26         4.2       Floating-Point Data Formats       29         4.2.1       Floating Point, Single Precision (32 bits)       29         4.2.1       Floating Point, Single Precision (64 bits)       29         4.2.2       Floating Point, Double Precision (64 bits)       29         4.2.3       Floating Point, Quad Precision (64 bits)       29         4.2.4       Floating-Point Data Alignment in Memory and Registers       30         4.3       SIMD Data Formats       31         4.3.1       Uint8 SIMD Data Format       32         4.3.2       Int16 SIMD Data Formats       32         4.3.3       Int32 SIMD Data Format       32         5       Registers       33         5.1       Reserved Register Fields       34         5.2       General-Purpose R Registers       35                                                                                                                                                                                                                                                                                                                                                                                                  |           | 4.1.2.1              | Unsigned Integer Byte, Halfword, and Word    | 28 |

| 4.1.3       Tagged Word (32 bits).       24         4.2       Floating-Point Data Formats       29         4.2.1       Floating Point, Single Precision (32 bits)       29         4.2.2       Floating Point, Double Precision (64 bits)       29         4.2.3       Floating Point, Quad Precision (64 bits)       29         4.2.4       Floating-Point Data Alignment in Memory and Registers       30         4.3       SIMD Data Formats       31         4.3.1       Uint8 SIMD Data Format       32         4.3.2       Int16 SIMD Data Formats       32         4.3.3       Int32 SIMD Data Format       32         5       Registers       33         5.1       Reserved Register Fields       34         5.2       General-Purpose R Registers       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           | 4.1.2.2              |                                              |    |

| 4.2       Floating-Point Data Formats       29         4.2.1       Floating Point, Single Precision (32 bits)       29         4.2.2       Floating Point, Double Precision (64 bits)       29         4.2.3       Floating Point, Quad Precision (64 bits)       29         4.2.4       Floating-Point Data Alignment in Memory and Registers       30         4.3       SIMD Data Formats       31         4.3.1       Uint8 SIMD Data Format       32         4.3.2       Int16 SIMD Data Formats       32         4.3.3       Int32 SIMD Data Format       32         5       Registers       33         5.1       Reserved Register Fields       34         5.2       General-Purpose R Registers       34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |                      |                                              |    |

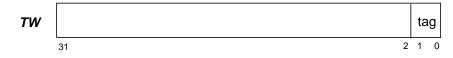

| 4.2.1Floating Point, Single Precision (32 bits)294.2.2Floating Point, Double Precision (64 bits)294.2.3Floating Point, Quad Precision (128 bits)304.2.4Floating-Point Data Alignment in Memory and Registers314.3SIMD Data Formats324.3.1Uint8 SIMD Data Format324.3.2Int16 SIMD Data Formats324.3.3Int32 SIMD Data Format325Registers335.1Reserved Register Fields345.2General-Purpose R Registers35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           | 4.1.3 Tagged         | Word (32 bits)                               | 28 |

| 4.2.2       Floating Point, Double Precision (64 bits)       29         4.2.3       Floating Point, Quad Precision (128 bits)       30         4.2.4       Floating-Point Data Alignment in Memory and Registers       31         4.3       SIMD Data Formats       31         4.3.1       Uint8 SIMD Data Format       32         4.3.2       Int16 SIMD Data Formats       32         4.3.3       Int32 SIMD Data Format       32         5       Registers       33         5.1       Reserved Register Fields       34         5.2       General-Purpose R Registers       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4.2 Fl    | oating-Point Data    | Formats                                      | 29 |

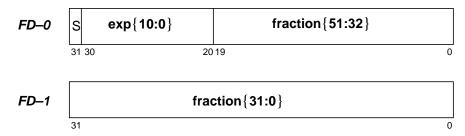

| 4.2.3       Floating Point, Quad Precision (128 bits).       30         4.2.4       Floating-Point Data Alignment in Memory and Registers       31         4.3       SIMD Data Formats       31         4.3.1       Uint8 SIMD Data Format       32         4.3.2       Int16 SIMD Data Formats       32         4.3.3       Int32 SIMD Data Format       32         5       Registers       33         5.1       Reserved Register Fields       34         5.2       General-Purpose R Registers       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           | 4.2.1 Floating       | Point, Single Precision (32 bits)            | 29 |

| 4.2.4       Floating-Point Data Alignment in Memory and Registers       33         4.3       SIMD Data Formats       33         4.3.1       Uint8 SIMD Data Format       32         4.3.2       Int16 SIMD Data Formats       32         4.3.3       Int32 SIMD Data Format       32         5       Registers       33         5.1       Reserved Register Fields       34         5.2       General-Purpose R Registers       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           | 4.2.2 Floating       | Point, Double Precision (64 bits)            | 29 |

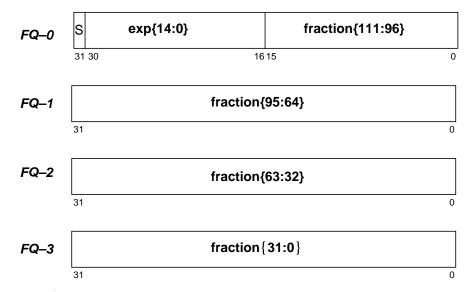

| 4.3       SIMD Data Formats       31         4.3.1       Uint8 SIMD Data Format       32         4.3.2       Int16 SIMD Data Formats       32         4.3.3       Int32 SIMD Data Format       32         5       Registers       33         5.1       Reserved Register Fields       34         5.2       General-Purpose R Registers       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |                      |                                              |    |

| 4.3.1       Uint8 SIMD Data Format       32         4.3.2       Int16 SIMD Data Formats       32         4.3.3       Int32 SIMD Data Format       32         5       Registers       33         5.1       Reserved Register Fields       34         5.2       General-Purpose R Registers       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           | 4.2.4 Floating       | Point Data Alignment in Memory and Registers | 31 |

| 4.3.2       Int16 SIMD Data Formats       32         4.3.3       Int32 SIMD Data Format       32         5       Registers       33         5.1       Reserved Register Fields       34         5.2       General-Purpose R Registers       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4.3 SI    | MD Data Formats      |                                              | 31 |

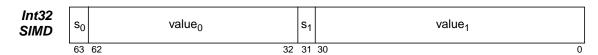

| 4.3.3       Int32 SIMD Data Format       32         5       Registers       33         5.1       Reserved Register Fields       34         5.2       General-Purpose R Registers       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           | 4.3.1 Uint8 SI       | MD Data Format                               | 32 |

| 5 Registers       33         5.1 Reserved Register Fields       34         5.2 General-Purpose R Registers       35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           | 4.3.2 Int16 SI       | MD Data Formats                              | 32 |

| 5.1    Reserved Register Fields    34      5.2    General-Purpose R Registers    35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           | 4.3.3 Int32 SI       | MD Data Format                               | 32 |

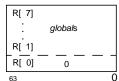

| 5.2 General-Purpose R Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5 Registe | rs                   |                                              | 33 |

| 5.2 General-Purpose R Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.1 Re    | eserved Register Fi  | elds                                         | 34 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |                      |                                              |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |                      |                                              |    |

| 5.2.2 Windowed R Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |                      |                                              |    |

| 5.2.3 Special R Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |                      |                                              |    |

| 5.3 Floating-Point Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5.3 Fl    | -                    | -                                            |    |

| 5.3.1 Floating-Point Register Number Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           | 0 0                  |                                              |    |

| 5.3.2 Double and Quad Floating-Point Operands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |                      |                                              |    |

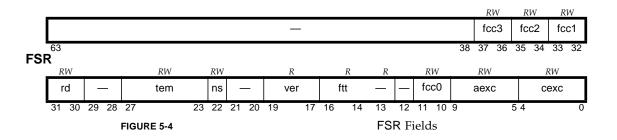

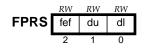

| 5.4 Floating-Point State Register (FSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5.4 Fl    |                      |                                              |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           | 0                    | 0                                            | 44 |

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           | 0                    | · · · · · · · · · · · · · · · · · · ·        | 45 |

| 5.4.2 Rounding Direction (rd)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |                      |                                              | 45 |

| 0 $(,)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           | 1                    |                                              | 45 |

| 5.4.3 Trap Enable Mask (tem) 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |                      |                                              | 45 |

| 5.4.3Trap Enable Mask (tem)455.4.4Nonstandard Floating-Point (ns)45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |                      |                                              | 46 |

| 5.4.3       Trap Enable Mask (tem)       45         5.4.4       Nonstandard Floating-Point (ns)       45         5.4.5       FPU Version (ver)       45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |                      |                                              | 48 |

| 5.4.3       Trap Enable Mask (tem)       45         5.4.4       Nonstandard Floating-Point (ns)       45         5.4.5       FPU Version (ver)       45         5.4.6       Floating-Point Trap Type (ftt)       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |                      |                                              | 48 |

| 5.4.3       Trap Enable Mask (tem)       45         5.4.4       Nonstandard Floating-Point (ns)       45         5.4.5       FPU Version (ver)       45         5.4.6       Floating-Point Trap Type (ftt)       46         5.4.7       Accrued Exceptions (aexc)       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           | 5.4.9 Floating       | -Point Exception Fields                      | 49 |

| 5.4.3       Trap Enable Mask (tem)       45         5.4.4       Nonstandard Floating-Point (ns)       45         5.4.5       FPU Version (ver)       45         5.4.6       Floating-Point Trap Type (ftt)       46         5.4.7       Accrued Exceptions (aexc)       48         5.4.8       Current Exception (cexc)       48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |                      |                                              | 50 |

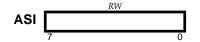

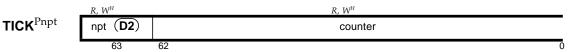

| 5.4.3       Trap Enable Mask (tem)       45         5.4.4       Nonstandard Floating-Point (ns)       45         5.4.5       FPU Version (ver)       45         5.4.6       Floating-Point Trap Type (ftt)       46         5.4.7       Accrued Exceptions (aexc)       48         5.4.8       Current Exception (cexc)       48         5.4.9       Floating-Point Exception Fields       49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5.5 A     | ncillary State Regis | ters                                         | 50 |

| 5.4.3       Trap Enable Mask (tem)       45         5.4.4       Nonstandard Floating-Point (ns)       45         5.4.5       FPU Version (ver)       45         5.4.6       Floating-Point Trap Type (ftt)       46         5.4.7       Accrued Exceptions (aexc)       48         5.4.8       Current Exception (cexc)       48         5.4.9       Floating-Point Exception Fields       49         5.4.10       FSR Conformance       50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           | , 0                  |                                              | 52 |

| 5.4.3Trap Enable Mask (tem)455.4.4Nonstandard Floating-Point (ns)455.4.5FPU Version (ver)455.4.6Floating-Point Trap Type (ftt)465.4.7Accrued Exceptions (aexc)465.4.8Current Exception (cexc)485.4.9Floating-Point Exception Fields495.4.10FSR Conformance505.5Ancillary State Registers50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |                      |                                              | 52 |

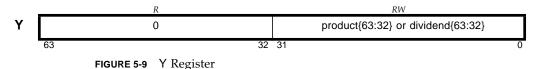

| 5.4.3       Trap Enable Mask (tem)       45         5.4.4       Nonstandard Floating-Point (ns)       45         5.4.5       FPU Version (ver)       45         5.4.6       Floating-Point Trap Type (ftt)       46         5.4.7       Accrued Exceptions (aexc)       46         5.4.8       Current Exception (cexc)       46         5.4.9       Floating-Point Exception Fields       49         5.4.10       FSR Conformance       50         5.5       Ancillary State Registers       50         5.5.1       32-bit Multiply/Divide Register (Y) (ASR 0)       52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           | 5.5.2.1              |                                              |    |

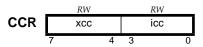

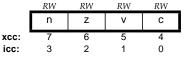

| 5.4.3       Trap Enable Mask (tem)       44         5.4.4       Nonstandard Floating-Point (ns)       44         5.4.5       FPU Version (ver)       44         5.4.6       Floating-Point Trap Type (ftt)       46         5.4.7       Accrued Exceptions (aexc)       46         5.4.8       Current Exception (cexc)       46         5.4.9       Floating-Point Exception Fields       49         5.4.10       FSR Conformance       50         5.5       Ancillary State Registers       50         5.5.1       32-bit Multiply/Divide Register (Y) (ASR 0)       52         5.5.2       Integer Condition Codes Register (CCR) (ASR 2)       52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |                      |                                              | 53 |

| 5.4.3       Trap Enable Mask (tem)       44         5.4.4       Nonstandard Floating-Point (ns)       44         5.4.5       FPU Version (ver)       44         5.4.6       Floating-Point Trap Type (ftt)       46         5.4.7       Accrued Exceptions (aexc)       48         5.4.8       Current Exception (cexc)       48         5.4.9       Floating-Point Exception Fields       49         5.4.10       FSR Conformance       50         5.5       Ancillary State Registers       50         5.5.1       32-bit Multiply/Divide Register (Y) (ASR 0)       52         5.5.2       Integer Condition Codes Register (CCR) (ASR 2)       52         5.5.2.1       Condition Codes (CCR.xcc and CCR.icc)       52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |                      |                                              |    |