# **Fujitsu SPARC M12 and Fujitsu M10 Server Architecture**

White Paper

Copyright © 2007, 2020, Fujitsu Limited. All rights reserved.

Oracle and/or its affiliates provided technical input and review on portions of this material.

Oracle and/or its affiliates and Fujitsu Limited each own or control intellectual property rights relating to products and technology described in this document, and such products, technology and this document are protected by copyright laws, patents, and other intellectual property laws and international treaties.

This document and the product and technology to which it pertains are distributed under licenses restricting their use, copying, distribution, and decompilation. No part of such product or technology, or of this document, may be reproduced in any form by any means without prior written authorization of Oracle and/or its affiliates and Fujitsu Limited, and their applicable licensors, if any. The furnishings of this document to you does not give you any rights or licenses, express or implied, with respect to the product or technology to which it pertains, and this document does not contain or represent any commitment of any kind on the part of Oracle or Fujitsu Limited or any affiliate of either of them.

This document and the product and technology described in this document may incorporate third-party intellectual property copyrighted by and/or licensed from the suppliers to Oracle and/or its affiliates and Fujitsu Limited, including software and font technology.

Per the terms of the GPL or LGPL, a copy of the source code governed by the GPL or LGPL, as applicable, is available upon request by the End User. Please contact Oracle and/or its affiliates or Fujitsu Limited. This distribution may include materials developed by third parties. Parts of the product may be derived from Berkeley BSD systems, licensed from the University of California.

UNIX is a registered trademark of The Open Group.

Oracle and Java are registered trademarks of Oracle and/or its affiliates.

Fujitsu and the Fujitsu logo are registered trademarks of Fujitsu Limited.

SPARC Enterprise, SPARC64, SPARC64 logo and all SPARC trademarks are trademarks or registered trademarks of SPARC International, Inc. in the United States and other countries and used under license.

Other names may be trademarks of their respective owners.

If this is software or related documentation that is delivered to the U.S. Government or anyone licensing it on behalf of the U.S. Government, the following notice is applicable:

U.S. GOVERNMENT END USERS: Oracle programs, including any operating system, integrated software, any programs installed on the hardware, and/or documentation, delivered to U.S. Government end users are "commercial computer software" pursuant to the applicable Federal Acquisition Regulation and agency-specific supplemental regulations. As such, use, duplication, disclosure, modification, and adaptation of the programs, including any operating system, integrated software, any programs installed on the hardware, and/or documentation, shall be subject to license terms and license restrictions applicable to the programs. No other rights are granted to the U.S. Government.

Disclaimer: The only warranties granted by Oracle and Fujitsu Limited, and/or any affiliate in connection with this document or any product or technology described herein are those expressly set forth in the license agreement pursuant to which the product or technology is provided.

EXCEPT AS EXPRESSLY SET FORTH IN SUCH AGREEMENT, ORACLE OR FUJITSU LIMITED, AND/OR THEIR AFFILIATES MAKE NO REPRESENTATIONS OR WARRANTIES OF ANY KIND (EXPRESS OR IMPLIED) REGARDING

SUCH PRODUCT OR TECHNOLOGY OR THIS DOCUMENT, WHICH ARE ALL PROVIDED AS IS, AND ALL EXPRESS OR IMPLIED CONDITIONS, REPRESENTATIONS AND WARRANTIES, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT, ARE DISCLAIMED, EXCEPT TO THE EXTENT THAT SUCH DISCLAIMERS ARE HELD TO BE LEGALLY INVALID. Unless otherwise expressly set forth in such agreement, to the extent allowed by applicable law, in no event shall Oracle or Fujitsu Limited, and/or any of their affiliates have any liability to any third party under any legal theory for any loss of revenues or profits, loss of use or data, or business interruptions, or for any indirect, special, incidental or consequential damages, even if advised of the possibility of such damages.

DOCUMENTATION IS PROVIDED "AS IS" AND ALL EXPRESS OR IMPLIED CONDITIONS, REPRESENTATIONS AND WARRANTIES, INCLUDING ANY IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT, ARE DISCLAIMED, EXCEPT TO THE EXTENT THAT SUCH DISCLAIMERS ARE HELD TO BE LEGALLY INVALID.

Fujitsu SPARCM12 is sold as SPARCM12 by Fujitsu in Japan.

Fujitsu SPARCM12 and SPARCM12 are identical products.

Fujitsu M10 is sold as SPARCM10 by Fujitsu in Japan.

Fujitsu M10 and SPARC M10 are identical products.

Copyright © 2007, 2020, Fujitsu Limited. Tous droits réservés.

Oracle et/ou ses affilies ont fourni et vérifié des données techniques de certaines parties de ce composant.

Oracle et/ou ses affilies et Fujitsu Limited détiennent et contrôlent chacun des droits de propriété intellectuelle relatifs aux produits et technologies décrits dans ce document. De même, ces produits, technologies et ce document sont protèges par des lois sur le droit d'auteur, des brevets, et d'autres lois sur la propriété intellectuelle et des traites internationaux.

Ce document, le produit et les technologies afférents sont exclusivement distribues avec des licences qui en restreignent l'utilisation, la copie, la distribution et la décompilation. Aucune partie de ce produit, de ces technologies ou de ce document ne peut être reproduite sous quelque forme que ce soit, par quelque moyen que ce soit, sans l'autorisation écrite préalable d'Oracle et/ou ses affilies et de Fujitsu Limited, et de leurs éventuels concédant de licence. Ce document, bien qu'il vous ait été fourni, ne vous confère aucun droit et aucune licence, exprès ou tacites, concernant le produit ou la technologie auxquels il se rapporte. Par ailleurs, il ne contient ni ne représente aucun engagement, de quelque type que ce soit, de la part d'Oracle ou de Fujitsu Limited, ou des sociétés affiliées de l'une ou l'autre entité.

Ce document, ainsi que les produits et technologies qu'il décrit, peuvent inclure des droits de propriété intellectuelle de parties tierces protèges par le droit d'auteur et/ou cèdes sous licence par des fournisseurs a Oracle et/ou ses sociétés affiliées et Fujitsu Limited, y compris des logiciels et des technologies relatives aux polices de caractères.

Conformément aux conditions de la licence GPL ou LGPL, une copie du code source régi par la licence GPL ou LGPL, selon le cas, est disponible sur demande par l'Utilisateur Final. Veuillez contacter Oracle et/ou ses affilies ou Fujitsu Limited. Cette distribution peut comprendre des composants développes par des parties tierces. Des parties de ce produit pourront être dérivées des systèmes Berkeley BSD licencies par l'Université de Californie.

UNIX est une marque déposée de The Open Group.

Oracle et Java sont des marques déposées d'Oracle Corporation et/ou de ses affilies.

Fujitsu et le logo Fujitsu sont des marques déposées de Fujitsu Limited.

SPARC Enterprise, SPARC64, le logo SPARC64 et toutes les marques SPARC sont utilisées sous licence et sont des marques déposées de SPARC International, Inc., aux Etats-Unis et dans d'autres pays.

Tout autre nommentionne peut correspondre à des marques appartenant à leurs propriétaires respectifs.

Si ce logiciel, ou la documentation qui l'accompagne, est concède sous licence au Gouvernement des Etats-Unis, ou à toute entité qui délivre la licence de ce logiciel ou l'utilise pour le compte du Gouvernement des Etats-Unis, la notice suivante s'applique:

U.S. GOVERNMENT END USERS: Oracle programs, including any operating system, integrated software, any programs installed on the hardware, and/or documentation, delivered to U.S. Government end users are "commercial computer software" pursuant to the applicable Federal Acquisition Regulation and agency-specific supplemental regulations. As such, use, duplication, disclosure, modification, and adaptation of the programs, including any operating system, integrated software, any programs installed on the hardware, and/or documentation, shall be subject to license terms and license restrictions applicable to the programs. No other rights are granted to the U.S. Government.

Avis de non-responsabilité: les seules garanties octroyées par Oracle et Fujitsu Limited et/ou toute société affiliée de l'une ou l'autre entité en rapport avec ce document ou tout produit ou toute technologie décrits dans les présentes correspondent aux garanties expressément stipulées dans le contrat de licence régissant le produit ou la technologie fournis.

SAUF MENTION CONTRAIRE EXPRESSEMENT STIPULEE AU DIT CONTRAT, ORACLE OU FUJITSU LIMITED ET/OU

LES SOCIETES AFFILIEES A L'UNE OU L'AUTRE ENTITE DECLINENT TOUT ENGAGEMENT OU GARANTIE, QUELLE QU'EN SOIT LA NATURE (EXPRESSE OU IMPLICITE) CONCERNANT CE PRODUIT, CETTE TECHNOLOGIE OU CE DOCUMENT, LESQUELS SONT FOURNIS EN L'ETAT. EN OUTRE, TOUTES LES CONDITIONS, DECLARATIONS ET GARANTIES EXPRESSES OU TACITES, Y COMPRIS NOTAMMENT TOUTE GARANTIE IMPLICITE RELATIVE A LA QUALITE MARCHANDE, A L'APTITUDE A UNE UTILISATION PARTICULIERE OU A L'ABSENCE DE CONTREFACON, SONT EXCLUES, DANS LA MESURE AUTORISEE PAR LA LOI APPLICABLE. Sauf mention contraire expressément stipulée dans ce contrat, dans la mesure autorisée par la loi applicable, en aucun cas Oracle ou Fujitsu Limited et/ou l'une ou l'autre de leurs sociétés affiliées ne sauraient être tenues responsables envers une quelconque partie tierce, sous quelque théorie juridique que ce soit, de tout manque à gagner ou de perte de profit, de problèmes d'utilisation ou de perte de données, ou d'interruptions d'activités, ou de tout dommage indirect, spécial, secondaire ou consécutif, même si ces entités ont été préalablement informées d'une telle éventualité.

LA DOCUMENTATION EST FOURNIE "EN L'ETAT" ET TOUTE AUTRE CONDITION, DECLARATION ET GARANTIE, EXPRESSE OU TACITE, EST FORMELLEMENT EXCLUE, DANS LA MESURE AUTORISEE PAR LA LOI EN VIGUEUR, Y COMPRIS NOTAMMENT TOUTE GARANTIE IMPLICITE RELATIVE A LA QUALITE MARCHANDE, A L'APTITUDE A UNE UTILISATION PARTICULIERE OU A L'ABSENCE DE CONTREFACON.

Au Japon, Fujitsu SPARCM12 est vendu en tant que SPARCM12 par Fujitsu.

Fujitsu SPARCM12 et SPARCM12 sont des produits identiques.

Au Japon, Fujitsu M10 est vendu en tant que SPARC M10 par Fujitsu.

Fujitsu M10 et SPARCM10 sont des produits identiques.

# Contents

| Coı  | ntents·····                                                                            | ···vii      |

|------|----------------------------------------------------------------------------------------|-------------|

| Intr | roduction·····                                                                         | 1           |

|      | Fujitsu SPARC M12 and Fujitsu M10 Providing Both High Performance and High Reliability | า<br>·····1 |

| 1.   | Fujitsu SPARC M12·····                                                                 | 4           |

|      | Product Lineup ······                                                                  |             |

|      | Fujitsu SPARC M12-1·····                                                               |             |

|      | Fujitsu SPARC M12-2·····                                                               | 7           |

|      | Fujitsu SPARC M12-2S·····                                                              | 8           |

| 2.   | Fujitsu M10·····                                                                       | 9           |

|      | Product Lineup ······                                                                  |             |

|      | Fujitsu M10-1 ·····                                                                    |             |

|      | Fujitsu M10-4 ·····                                                                    | ··· 12      |

|      | Fujitsu M10-4S ·····                                                                   | ··· 13      |

| 3.   | SPARC64 XII, SPARC64 X+, and SPARC64 X Processors ······                               | 15          |

| 4.   | System Architecture                                                                    | 17          |

|      | System Interconnect·····                                                               |             |

|      | 1. System Bus ·····                                                                    |             |

|      | 2. Fujitsu SPARC M12-1 Interconnect Architecture·····                                  | ··· 19      |

|      | 3. Fujitsu SPARC M12-2 Interconnect Architecture·····                                  | 20          |

|      | 4. Fujitsu SPARC M12-2S Interconnect Architecture·····                                 | ··· 21      |

|      | 5. Fujitsu M10-1 Interconnect Architecture·····                                        |             |

|      | 6. Fujitsu M10-4 Interconnect Architecture·····                                        |             |

|      | 7. Fujitsu M10-4S Interconnect Architecture·····                                       |             |

|      | 8. System Interconnect Reliability Features ·····                                      | 29          |

|      | Memory ····                                                                            |             |

|      | 1. Memory Mirroring·····                                                               |             |

|      | System Clock ·····                                                                     |             |

|      | I/O Bus                                                                                |             |

|      | 1. I/O Subsystem Architecture                                                          |             |

|      | 2. Fujitsu SPARC M12-1 I/O Subsystem ·····                                             |             |

|      | 3. Fujitsu SPARC M12-2 I/O Subsystem ·····                                             |             |

|      | 4. Fujitsu SPARC M12-2S I/O Subsystem ·····                                            |             |

|      | 5. Fujitsu M10-1 I/O Subsystem·····                                                    |             |

|      | 6. Fuiitsu M10-4 I/O Subsystem·····                                                    | 3/          |

|    | 7. Fujitsu M10-4S VO Subsystem·····                                          | 38    |

|----|------------------------------------------------------------------------------|-------|

|    | 8. Internal Drives and Peripherals ······                                    | 39    |

|    | 9. PCI Expansion Unit·····                                                   |       |

|    | Cooling·····                                                                 |       |

|    | High-Efficiency Power Supplies ·····                                         |       |

| 5. | System Management ·····                                                      | ·· 44 |

|    | Reliability, Availability, and Serviceability                                | ·· 44 |

|    | Redundant and Hot-Swappable Components · · · · · · · · · · · · · · · · · · · | ·· 45 |

|    | 2. Partitioning Feature·····                                                 |       |

|    | 3. Advanced Reliability Features·····                                        |       |

|    | 4. Error Detection, Diagnosis, and Recovery·····                             | ·· 47 |

|    | System Management·····                                                       |       |

|    | eXtended System Control Facility                                             |       |

|    | 2. Redundant XSCF                                                            | _     |

|    | 3. XSCF Control Package                                                      |       |

|    | 4. Role-based System Management                                              |       |

|    | Oracle Enterprise Manager Ops Center 12c     Eco-Friendly Computing          | ·· 50 |

|    |                                                                              |       |

| 6. | Oracle Solaris 11 Operating System ·····                                     |       |

|    | Oracle Solaris ZFS·····                                                      | _     |

|    | Oracle VM Server for SPARC                                                   |       |

|    | Oracle Solaris Zones ······ Image Packaging System ······                    |       |

|    | Boot Environment·····                                                        |       |

| _  |                                                                              | 50    |

| 7. | Technological Enhancements of the SPARC64 XII, SPARC64 X+, and               |       |

|    | SPARC64X Processors                                                          |       |

|    | Microarchitecture                                                            |       |

|    | 1. Chip Configuration                                                        |       |

|    | 2. Core Microarchitecture                                                    |       |

|    | Interface Between Chips  Extended Instruction Set Architecture               |       |

|    | HPC-ACE                                                                      |       |

|    | 2. SWoC (Software on Chip)·····                                              |       |

|    | Reliability, Availability, and Serviceability Features ·········             |       |

|    | 1. Error Marking                                                             |       |

|    | Internal RAM Reliability and Availability Features                           |       |

|    | Internal Register and Execution Unit Reliability Features                    |       |

|    | Synchronous Update Method and Instruction Retry                              |       |

|    | 5. Increased Serviceability ······                                           | ·· 74 |

| 8. | Conclusion ·····                                                             |       |

| υ. | - OTTOINGTOTT                                                                | , ,   |

# Introduction

# Fujitsu SPARC M12 and Fujitsu M10 Providing Both High Performance and High Reliability

To respond to rapidly changing business environments, IT infrastructures must provide higher speed, reliability, and operational efficiency as well as optimized performance. The Fujitsu SPARC M12 and Fujitsu M10 provide the total platform required in modern IT infrastructures with leading technologies including a high-performance processor, cutting-edge semiconductor advancements, and the high reliability and high quality inherited from Fujitsu's mainframes and SPARC Enterprise M-series. The Fujitsu SPARC M12 and Fujitsu M10 have further enhanced system reliability, flexibility, and scalability to meet the demands of cloud computing environments.

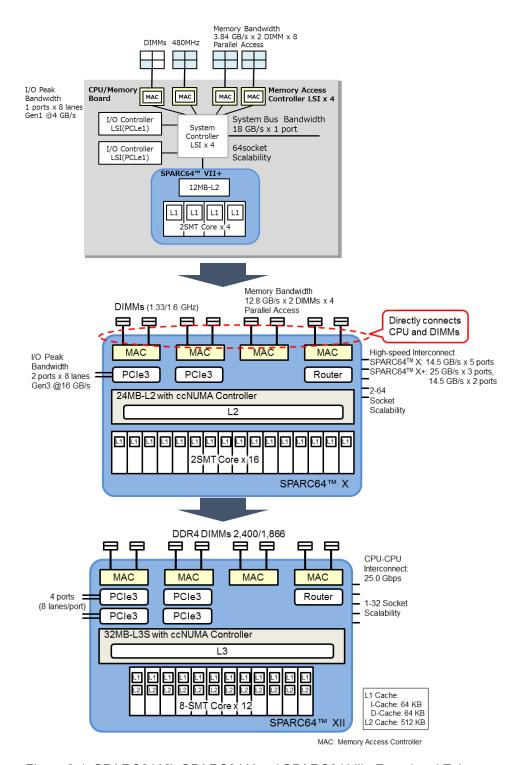

# Improved System Performance With the SPARC64 $^{\text{TM}}$ XII, SPARC64 $^{\text{TM}}$ X+, and SPARC64 $^{\text{TM}}$ X

Fujitsu has developed the new SPARC64 XII (twelve) processor, which inherits the high performance and high reliability of the SPARC64 X+ (ten plus) processor and SPARC64 X (ten) processor.

The SPARC64 XII processor mounted in the Fujitsu SPARC M12 provides high core performance, which accelerates the database/DWH processing of customers' mission-critical systems.

The Fujitsu M10 is offered with two kinds of processors, SPARC64 X+ and SPARC64 X. With these processors, customers are able to select the most appropriate engine depending on the workload required.

#### - System on chip

With the SPARC64 XII, SPARC64 X+, and SPARC64 X processors having been developed for UNIX servers, peripheral LSIs are consolidated into the processors.

#### - Software on chip

Many processing functions that were traditionally handled by software have been built into the processor hardware, by adding multiple, dedicated instructions. For handling big data

1

analytics and analysis processing, the number of concurrent processes has increased.

#### - Cooling technology

Fujits u's proprietary cooling technologies get the maximum performance out of the processor (Liquid Loop Cooling (LLC) and Vapor and Liquid Loop Cooling (VLLC), a newly introduced cooling technology).

These technologies achieve significant improvements in processing speed (throughput) and overall performance.

# Fujitsu SPARC M12 and Fujitsu M10: Most Appropriate for Mission-Critical Systems and Real-Time Information Analysis

The processors are interconnected with the Fujitsu SPARC M12 or Fujitsu M10 using a cutting-edge fast interconnect technology. Moreover, the Fujitsu SPARC M12-2S and Fujitsu M10-4S adopt the Building Block (BB) expansion method (\*1), which can significantly enhance performance and functionality. A maximum of 16 servers can be interconnected to build a single, large system. Up to 16 Fujitsu SPARC M12-2S chass is with up to 32 CPUs/3072 threads (up to 16 Fujitsu M10-4S chass is with up to 64 CPUs/2048 threads) deliver the highest performance in an extremely flexible and scalable system.

From a small-scale configuration at installation, which reduces the initial investment, the system can expand to meet increases in demand, such as to integrate an information analysis system with a database system to run real-time analysis.

These features make the Fujitsu SPARC M12 and Fujitsu M10 the most appropriate servers for datacenters in the cloud computing era.

#### Fujitsu SPARC M12 and Fujitsu M10: Better Installation

The Fujitsu SPARC M12 and Fujitsu M10 also benefit from increased ease of installation. With peripheral LSIs consolidated into their SPARC64 XII, SPARC64 X+, and SPARC64 X processors, the Fujitsu SPARC M12 and Fujitsu M10 are very densely packaged servers delivering substantial spaces avings.

The Fujitsu SPARC M12 and Fujitsu M10 housing the SPARC64 XII, SPARC64 X+, and

<sup>\*1</sup> The Building Block method allows common servers (blocks) containing CPUs, memory, and I/O expansion slots to be connected like children's toy blocks being stacked up.

SPARC64 X processors merge numerous hardware and software technologies to provide customers with the most appropriate solution for their ever-growing IT infrastructures.

# 1.Fujitsu SPARC M12

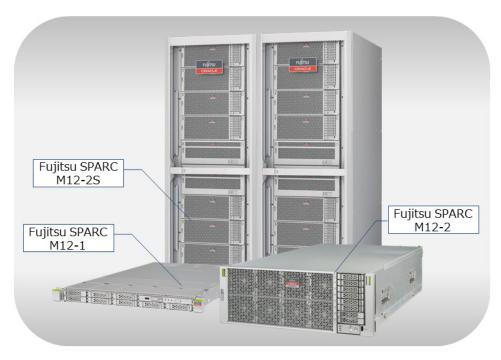

## **Product Lineup**

The Fujitsu SPARC M12 is the optimal product for a broad range of needs, like for a database or analytics infrastructure.

- Fujitsu SPARC M12-1: An entry-level server that offers high performance and high reliability in a space-saving 1U chassis

- Fujitsu SPARC M12-2: A mid-range server perfect for system consolidation, such as database or analytics consolidation

- Fujitsu SPARC M12-2S: Capable of covering a broad range of needs from mid-range to high-end

Figure 1-1. Fujitsu SPARC M12 Product Lineup

Table 1-1. Fujitsu SPARC M12 Specifications

|                            |                                                             | Fujitsu SPARC M12-1                                  | Fujitsu SPARC M12-2                                                                                                             | Fujitsu SPARC M12-2S<br>(1BB)                                                                                                   | Fujitsu SPARC<br>M12-2S<br>(16BB)                                                                                                   |

|----------------------------|-------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| SPARC64 XII<br>Processor   | Frequency L3 cache CPUs Cores Threads                       | 3.2 GHz<br>16 MB<br>1<br>6<br>48                     | 3.9 GHz 32 MB 1 or 2 12 (per processor) 96 (per processor)                                                                      | 4.25 GHz 32 MB 1 or 2 12 (per processor) 96 (per processor)                                                                     | 4.25 GHz 32 MB Up to 32 Up to 384 Up to 3072                                                                                        |

| Memory                     | Maximum size<br>Mounted memory<br>modules, maximum          | 1 TB                                                 | 3 TB (24 memory slots/processor) 2 TB (16 memory slots/processor) 48 (24 memory slots/processor) 32 (16 memory slots/processor) | 3 TB (24 memory slots/processor) 2 TB (16 memory slots/processor) 48 (24 memory slots/processor) 32 (16 memory slots/processor) | 48 TB (24 memory slots/processor) 32 TB (16 memory slots/processor) 768 (24 memory slots/processor) 512 (16 memory slots/processor) |

| Internal Storage           | Interface<br>Built-in disks                                 | SAS<br>8                                             | SAS<br>8                                                                                                                        | SAS<br>8                                                                                                                        | SAS<br>128                                                                                                                          |

| PCIe Slot                  | Interface Built-in PCIe slots Built-in PCIe slots (maximum) | PCI Express 3.0 3 33 (*1) With 3 PCI Expansion Units | PCI Express 3.0  11  91 (*1) With 8 PCI Expansion Units                                                                         | PCI Express 3.0<br>8<br>88 (*1)<br>With 8 PCI Expansion<br>Units                                                                | PCI Express 3.0<br>128<br>1,408 (*1)<br>With 128 PCI<br>Expansion Units                                                             |

| I/O Interface              | 10 Gb Ethernet ports<br>SAS ports<br>USB ports              | 4<br>1<br>2                                          | 4<br>1<br>2                                                                                                                     | 4<br>1<br>2                                                                                                                     | 64<br>16<br>32                                                                                                                      |

| Rack Units                 |                                                             | 1U                                                   | 4U                                                                                                                              | 4U                                                                                                                              | 40U x 2<br>(including XB-Boxes)                                                                                                     |

| Virtualization<br>Function | Physical partitions  Logical domains,  maximum              | 1<br>48                                              | 1<br>192                                                                                                                        | 1 (1 partition per BB)<br>192                                                                                                   | Up to 16 256 per physical partition                                                                                                 |

<sup>\*1</sup> When the number of mounted CPUs has reached the maximum and the OS versions on the control domain, root domain, and I/O domain are all Oracle Solaris 11

## Fujitsu SPARC M12-1

The Fujitsu SPARC M12-1 is an entry-level server that offers high performance and high reliability in a space-saving chassis measuring one rack unit (1U).

The server basically comes with a single high-performance CPU with up to six cores, and supports up to 1 TB of memory and up to eight internal storage slots (supporting hard disk drives and SSDs). The server includes three PCI Express slots. For further expansion, PCI Expansion Units can be added to provide up to 33 internal I/O slots. Thus, the server provides mid-range class scalability. The server has a redundant configuration with two built-in power supplies and seven built-in fan units.

A system can be purchased with the minimum required CPU resources. Then, as needed, the CPU resources can be expanded in a step-by-step manner with the purchase of CPU Activations (CPU Rights to Use). In addition, server virtualization and system consolidation are realized through both Oracle Solaris Zones and Oracle VM Server for SPARC. The Fujitsu SPARC M12-1 can build on the initial investment reductions and step-by-step processing expansion, so TCO can be optimized even by this entry-level server.

## Fujitsu SPARC M12-2

The Fujitsu SPARC M12-2 is a high-performance and highly reliable mid-range server that is appropriate for database integration and consolidation of databases and analytics. Its mainframe-class reliability is suitable for customers' mission-critical business.

The Fujitsu SPARC M12-2 occupies 4 rack units (4U) and supports up to 2 CPUs (24 cores), up to 3 TB (24 memory slots per processor) of memory, and up to 8 internal storage slots supporting hard disk drives and SSDs). The Fujitsu SPARC M12-2 also includes 11 PCI Express slots. To support further I/O expansion, PCI Expansion Units can be connected to provide up to 91 PCI Express slots. Four power supply units (two per group) provide redundant power to the server. The Vapor and Liquid Loop Cooling (VLLC) system, a redundant high-efficiency cooling technology developed by Fujitsu, and eight fan units cool the server.

A system can be purchased with the minimum required CPU resources. Then, as needed, the CPU resources can be expanded in a step-by-step manner with the purchase of CPU Activations (CPU Rights to Use). In addition, both Oracle Solaris Zones and Oracle VM Server for SPARC allow flexible changes to a virtualized configuration according to variation requests for the system. Processing expansion is realized in the Fujitsu SPARC M12-2 by expanding CPU capacity from one CPU to two CPUs.

## Fujitsu SPARC M12-2S

The Fujitsu SPARC M12-2S provides the world's highest level scalability and flexibility, covering a broad range of needs, from mid-range to high-end. This model is also capable of large-scale consolidation including mission-critical databases.

In addition to high performance and high reliability, the Fujitsu SPARC M12-2S provides flexible scalability by virtue of the Building Block expansion method. With an expansion rack installed, a customer can freely combine scale-up configurations with scale-out configurations best suited for distributed parallel processing while continuing business operations. With 2 expansion racks, the customer can scale up to 16 interconnected Building Blocks without shutting down the entire system.

Fujitsu high-speed interconnect technology provides the connection between Fujitsu SPARC M12-2S Building Block chassis and achieves linear performance improvement up to the maximum 16BB configuration. A system can be purchased with the minimum required CPU, memory, PCI Express slot, and disk bay resources. Then, as needed, the customer can increase capacity by adding more Fujitsu SPARC M12-2S chassis. The CPU resources can also be expanded in a step-by-step manner with the purchase of CPU Activations (CPU Rights to Use) to achieve finer granularity expansion than by adding whole CPU chips.

# 2. Fujitsu M10

## **Product Lineup**

The Fujitsu M10 covers a product lineup that is applicable to a broad range of industries.

- Fujitsu M10-1: An entry-level server in a space-saving 1U chassis

- Fujitsu M10-4: A mid-range server perfect for system consolidation

- Fujitsu M10-4S: Capable of covering a broad range of needs, from mid-range to high-end

Figure 2-1. Fujitsu M10 Product Lineup

Table 2-1. Fujitsu M10 Specifications

|                              |                                                             | Fujitsu M10-1                                                            | Fujitsu M10-4                                                                       | Fujitsu M10-4S<br>(1BB)                                          | Fujitsu M10-4S<br>(16BB)                                             |

|------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------|

| SPARC64 X+<br>Processor (*1) | Frequency<br>L2 cache<br>CPUs<br>Cores<br>Threads           | 2.8 GHz/3.2 GHz/3.7 GHz<br>22 MB/22 MB/24 MB<br>1<br>16/16/8<br>32/32/16 | 3.4 GHz/3.7 GHz<br>24 MB<br>2 or 4<br>16/8 (per processor)<br>32/16 (per processor) | 3.7 GHz 24 MB 2 or 4 16 (per processor) 32 (per processor)       | 3.7 GHz<br>24 MB<br>Up to 64<br>Up to 1024<br>Up to 2048             |

| SPARC64 X<br>Processor (*1)  | Frequency<br>L2 cache<br>CPUs<br>Cores<br>Threads           | 2.8 GHz<br>22 MB<br>1<br>16<br>32                                        | 2.8 GHz 24 MB 2 or 4 16 (per processor) 32 (per processor)                          | 3.0 GHz 24 MB 2 or 4 16 (per processor) 32 (per processor)       | 3.0 GHz<br>24 MB<br>Up to 64<br>Up to 1024<br>Up to 2048             |

| Memory                       | Maximum size<br>Mounted memory<br>modules, maximum          | 1 TB<br>16                                                               | 4 TB<br>64                                                                          | 4 TB<br>64                                                       | 64 TB<br>1024                                                        |

| Internal Storage             | Interface<br>Built-in disks                                 | SAS<br>8                                                                 | SAS<br>8                                                                            | SAS<br>8                                                         | SAS<br>128                                                           |

| PCIe Slot                    | Interface Built-in PCIe slots Built-in PCIe slots (maximum) | PCI Express 3.0 3 23 With 2 PCI Expansion Units                          | PCI Express 3.0  11  71 (*2) With 6 PCI Expansion Units                             | PCI Express 3.0<br>8<br>58 (*2)<br>With 5 PCI Expansion<br>Units | PCI Express 3.0<br>128<br>928 (*2)<br>With 80 PCI<br>Expansion Units |

| I/O Interface                | 1 Gb Ethernet ports<br>SAS ports<br>USB ports               | 4<br>1<br>2                                                              | 4<br>1<br>2                                                                         | 4<br>1<br>2                                                      | 64<br>16<br>32                                                       |

| Rack Units                   |                                                             | 1U                                                                       | 4U                                                                                  | 4U                                                               | 40U x 2<br>(including XB-Boxes)                                      |

| Virtualization<br>Function   | Physical partitions<br>Logical domains,<br>maximum          | 1<br>32                                                                  | 1<br>128                                                                            | 1 (1 per BB)<br>128                                              | Up to 16<br>256 per physical<br>partition                            |

<sup>\*1</sup> Either the SPARC64 X+ or SPARC64 X processor can be mounted. A SPARC64 X Fujitsu M10-4S Building Block can be connected with a SPARC64 X+ Fujitsu M10-4S Building Block.

<sup>\*2</sup> When the number of mounted CPUs has reached the maximum

### Fujitsu M10-1

The Fujitsu M10-1 is an entry-level server, in a space-saving chass is measuring one rack unit (1U), providing excellent performance and reliability appropriate for datacenter consolidation and virtualization.

The server basically comes with a single high-performance CPU with up to 16 cores, and supports up to 1 TB of memory and up to 8 internal storage slots (supporting hard disk drives and SSDs). The Fujitsu SPARC M12-2 also includes 3 PCI Express slots. To support further I/O expansion, PCI Expansion Units can be connected to provide up to 23 PCI Express slots. Two power supplies and seven fan units power and cool the server with built-in redundancy.

A system can be purchased with the minimum required CPU resources. Then, as needed, the CPU resources can be expanded in a step-by-step manner with the purchase of CPU Activations (CPU Rights to Use). In addition, server virtualization and system consolidation are realized through both Oracle Solaris Zones and Oracle VM Server for SPARC. The Fujitsu M10-1 can build on the initial investment reductions and step-by-step processing expansion, so TCO can be optimized even by this entry-level server.

#### Fujitsu M10-4

The Fujitsu M10-4 is a high-performance and highly reliable mid-range server that is appropriate for datacenter consolidation and virtualization tasks requiring more processors, memory, and I/O capacity than are available in the Fujitsu M10-1 model. It provides the flexibility, scalability, and reliability required to support customers' mission-critical businesses.

The Fujitsu SPARC M12-2 occupies 4 rack units (4U) and supports up to 4 CPUs (up to 64 cores total), up to 4 TB of memory, and up to 8 internal storage slots (supporting hard disk drives and SSDs). The Fujitsu M10-4 also includes 11 PCI Express slots. To support further I/O expansion, PCI Expansion Units can be connected to provide up to 71 PCI Express slots. Two power supply units provide redundant power to the server. The Liquid Loop Cooling (LLC) systemand five fan units cool the server.

A system can be purchased with the minimum required CPU resources. Then, as needed, the CPU resources can be expanded in a step-by-step manner with the purchase of CPU Activations (CPU Rights to Use). In addition, server virtualization and system consolidation are realized through both Oracle Solaris Zones and Oracle VM Server for SPARC. The Fujitsu M10-4 builds on the initial investment reductions and step-by-step processing expansion found in the Fujitsu M10-1. The server expands CPU capacity from two CPUs to up to four CPUs, offering the maximum utilization of memory and I/O.

## Fujitsu M10-4S

The Fujitsu M10-4S provides the world's highest scalability and flexibility, and covers a broad range of computing needs, from mid-range to high-end. The Fujitsu M10-4S is the most appropriate for use in cloud computing and big data processing infrastructures that are currently large scale or have the potential to grow significantly over time.

In addition to the high performance and high reliability found in the Fujitsu M10 model, the Fujitsu M10-4S provides flexible scalability by virtue of the Building Block expansion method. With an expansion rack installed, a customer can freely combine scale-up configurations with scale-out configurations best suited for distributed parallel processing without interrupting working partitions. With 2 expansion racks, the customer can scale up to 16 interconnected Building Blocks without shutting down the entire system.

The proprietary Fujitsu interconnect technology that provides the connection between Building Blocks achieves linear performance improvement up to the maximum 16BB configuration. A system can be purchased with the minimum required CPU, memory, PCI Express slot, and disk bay resources. Then, as needed, the customer can increase capacity by adding more Fujitsu M10-4S chassis. The CPU resources can also be expanded in a step-by-step manner with the purchase of CPU Activations (CPU Rights to Use) to achieve finer granularity expansion than

by adding whole CPU chips.

Furthermore, additional SPARC64 X Fujitsu M10-4S Building Blocks can be connected to not only SPARC64 X Fujitsu M10-4S Building Blocks but also SPARC64 X+ Fujitsu M10-4S Building Blocks.

Even a system that already uses a Fujitsu M10-4S with a mounted SPARC64 X+ instead of a Fujitsu M10-4S with a mounted SPARC64 X can be upgraded to a higher-performance system without wasting the Fujitsu M10-4S with the mounted SPARC64 X.

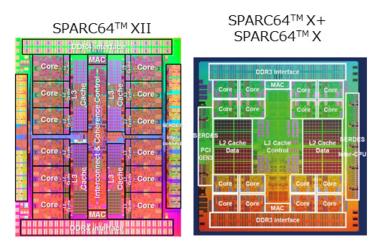

# 3. SPARC64 XII, SPARC64 X+, and SPARC64 X Processors

The SPARC64 XII is the latest of the processors developed by Fujitsu to combine high performance and high reliability for UNIX servers. The processors feature high core performance, high operating frequencies, multi-core and multithreading features, and high memory throughput. Furthermore, the SPARC64 XII can connect up to 32 CPU chips in a single system, and the SPARC64 X+ or SPARC64 X can connect up to 64 CPU chips, offering extremely high performance and scalability. Fujitsu's heritage of mainframe-class high reliability technology is found throughout the processors and corresponding systems.

The SPARC64 XII, SPARC64 X+, and SPARC64 X inherit the robust high-reliability technologies found in previous SPARC64 processors and, at the same time, offer multiple functional enhancements. The enhancements extend beyond microarchitecture improvements, such as significantly higher core counts and the consolidation of peripheral LSI functions into the processor, to include register extensions and significant instruction set enhancements that improve SIMD instruction-based cryptographic and database processing performance.

The SPARC64 XII, SPARC64 X+, and SPARC64 X consolidate peripheral LSI functions into the processor, leading directly to faster processing and improvement in performance per Watt. Compared to the SPARC64 VII+, the SPARC64 X delivers approximately twice the performance per CPU core, and a 7.5-times improvement in per-processor performance. The SPARC64 X+ achieves a further improvement of 2.4 times the performance per CPU core and 9.5 times the performance per processor. Compared to the SPARC64 X+, the SPARC64 XII provides approximately 2.5 times the performance per CPU core and approximately twice the performance per processor (as measured with SPECint rate).

The significant technological enhancements of the SPARC64 XII, SPARC64 X+, and SPARC64 X are explained in detail in "Chapter 7. Technological Enhancements of the SPARC64 XII, SPARC64 X+, and SPARC64 X Processors."

Figure 3-1. SPARC64 XII, SPARC64 X and SPARC64 VII+ Functional Enhancement

# 4. System Architecture

In the Fujitsu SPARC M12 and Fujitsu M10, the processors, system interconnects, and memory and I/O subsystems work in concert to create a scalable, high-performance platform ready to address a wide range of workloads, from consolidation of general-purpose enterprise computing to the fastest, largest, and most secure database processing.

The design of the Fujitsu SPARC M12 and Fujitsu M10 focuses on high reliability, and places emphasis on maximizing the merits of memory locality in a ccNUMA architecture to deliver outstanding performance. The characteristics and capabilities of every subsystem within the Fujitsu SPARC M12 and Fujitsu M10 work toward this goal. A high-bandwidth system bus, the powerful SPARC64 XII, SPARC64 X+, and SPARC64 X processors, dense memory support, and fast PCI Express combine within the Fujitsu SPARC M12 and Fujitsu M10 to deliver the highest levels of uptime and throughput, as well as dependable scaling for enterprise applications.

## System Interconnect

The system interconnect underpins the highest levels of performance, scalability, and reliability for the Fujitsu SPARC M12 and Fujitsu M10. Multiple system controllers and crossbar units within the Fujitsu SPARC M12 and Fujitsu M10 provide point-to-point connections between the CPUs, memory, and I/O subsystems. Offering more than one bus route between components enhances performance and allows system operation to continue in the event of a fault.

#### System Bus

High-end systems containing dozens of CPUs provide scalability only if all processors are able to actually contribute to the performance of the application. The ability to deliver near-linear scalability and fast, predictable performance for a broad set of applications rests largely on the capabilities of the system bus. The Fujitsu SPARC M12 and Fujitsu M10 utilize a system interconnect designed to deliver massive bandwidth and consistent, low latency between components. The system bus benefits IT operations by delivering balanced and predictable performance to application workloads.

The interconnect design maximizes the overall performance of the Fujitsu SPARC M12 and Fujitsu M10. Implemented as point-to-point connections that utilize packet-switching technology, this system bus provides fast response times by transmitting multiple data streams.

Packet switching allows the interconnect to operate at much higher system-wide throughput by eliminating "dead" cycles on the bus. All routes are unidirectional, non-contentious paths with multiplexed address, data, and control in each direction.

System controllers within the interconnect architecture of the Fujitsu SPARC M12 and Fujitsu M10 direct traffic between CPUs in each chass is, memory, I/O subsystems, and interconnect paths.

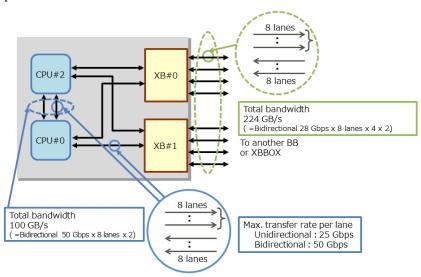

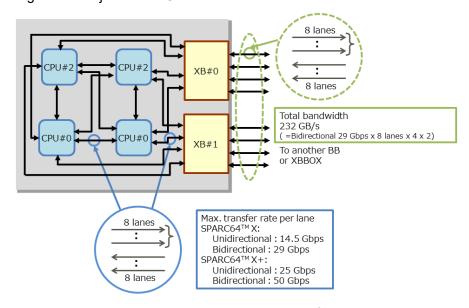

Figure 4-1. Fujitsu SPARC M12 Bandwidth and Data Transfer Rate

Figure 4-2. Fujitsu M10 Bandwidth and Data Transfer Rate

#### 2. Fujitsu SPARC M12-1 Interconnect Architecture

The Fujitsu SPARC M12-1 is implemented on a single physical system board with one SPARC64 XII processor. The memory access, I/O, and system controllers are embedded in the processor. The processor is connected directly to DIMMs and PCI Express switches.

An architecture diagram of the Fujitsu SPARCM12-1 is shown in Figure 4-3.

Figure 4-3. Fujitsu SPARC M12-1 Interconnect Architecture

#### 3. Fujitsu SPARC M12-2 Interconnect Architecture

Each Fujitsu SPARC M12-2 supports one SPARC64 XII processor by default and accommodates up to two processors. The memory access, I/O, and system controllers are embedded in the processor. Each processor connects to DIMMs and PCI Express switches, and both processors are interconnected by the system bus. To increase I/O bus bandwidth and protect against processor failure, each PCI Express switch connects to two SPARC64 X+ or SPARC64 X processors (Figure 4-4).

Figure 4-4. Fujitsu SPARC M12-2 Interconnect Architecture

#### 4. Fujitsu SPARC M12-2S Interconnect Architecture

The Fujitsu SPARC M12-2S implements crossbar units in the server and crossbar boxes in order to connect multiple Fujitsu SPARC M12-2S chass is using the Building Block method. Each Fujitsu SPARC M12-2S supports one SPARC64 XII processor by default and accommodates up to two processors. The memory access, I/O, and system controllers are embedded in the processor. Each processor connects to DIMMs and PCI Express switches, and both processors are interconnected by the system bus. To increase I/O bus bandwidth and protect against processor failure, each PCI Express switch connects to two SPARC64 X+ or SPARC64 X processors (Figure 4-5).

Figure 4-5. Fujitsu SPARC M12-2S Interconnect Architecture

The Fujitsu SPARC M12-2S, adopting the Building Block method, implements crossbar units to connect the system buses between Fujitsu SPARC M12-2S chass is. The system buses support low-latency and high-throughput data transfers.

To improve performance, the physical addressing of memory in the Building Block configuration is evenly spread out across the system controllers of all Fujitsu SPARC M12-2S chassis.

The SPARC64 XII processor has a direct connection to the crossbar units, minimizing the latency of data transfers over multiple Fujitsu SPARC M12-2S chass is. You can use point-to-point connection to directly connect the built-in crossbar units of up to four Fujitsu SPARC M12-2S chass is and expand to up to eight CPU chips (Figure 4-6). With system configurations scalable up to 16 Fujitsu SPARC M12-2S chass is, each chass is is connected to all other chass is via crossbar boxes (Figure 4-7). The system interconnect used in the Fujitsu SPARC M12-2S delivers as much as 5,453 GB/s of peak bandwidth and provides near-linear scalability.

Figure 4-6. System Configuration Directly Connecting Servers (Fujitsu SPARC M12-2S 4BB)

Note: This figure shows only the connection between the BB#0 ports and XB-BOX (0 System). The BB#1 ports and XB-BOX (1 System) are connected in the same way.

Figure 4-7. System Configuration of Connections via Crossbar Boxes (Fujitsu SPARC M12-2S 16BB)

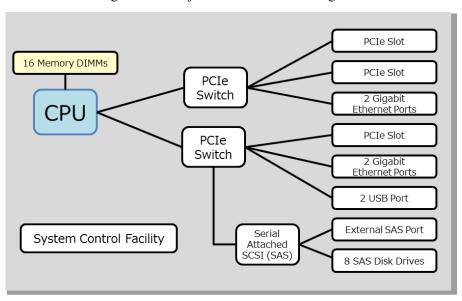

#### 5. Fujitsu M10-1 Interconnect Architecture

The Fujitsu M10-1 is implemented on a single physical system board. One SPARC64 X or SPARC64 X processor is mounted. The memory access, I/O, and system controllers are embedded in the processor. The SPARC64 X+ or SPARC64 X is connected to DIMMs and PCI Express switches.

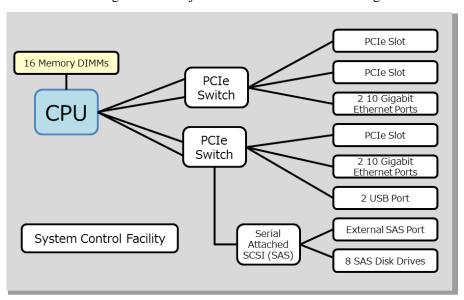

An architecture diagram of the Fujitsu M10-1 is shown in Figure 4-8.

Figure 4-8. Fujitsu M10-1 Interconnect Architecture

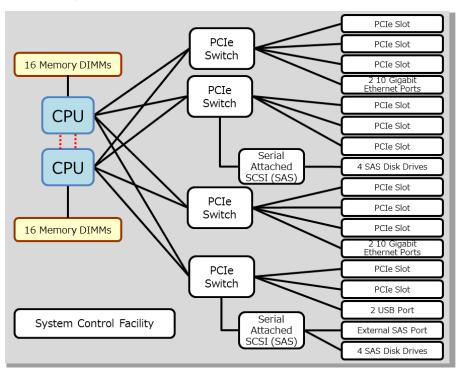

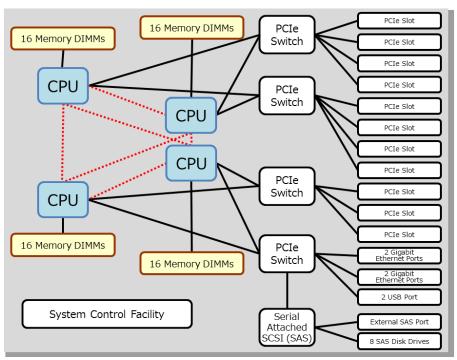

#### 6. Fujitsu M10-4 Interconnect Architecture

The Fujitsu M10-4 is implemented on two physical system boards, which function as a single logical system board. The Fujitsu M10-4 supports up to either four SPARC64 X+ processors or four SPARC64 X processors; and as with the Fujitsu M10-1, the memory access, I/O, and system controllers are embedded in the CPU. Each controller connects to DIMMs and PCI Express switches, and all four SPARC64 X+ or SPARC64 X processors are interconnected. To increase I/O bus bandwidth and protect against processor failure, each PCI Express switch connects to two SPARC64 X+ or SPARC64 X processors (Figure 4-9).

Figure 4-9. Fujitsu M10-4 Interconnect Architecture

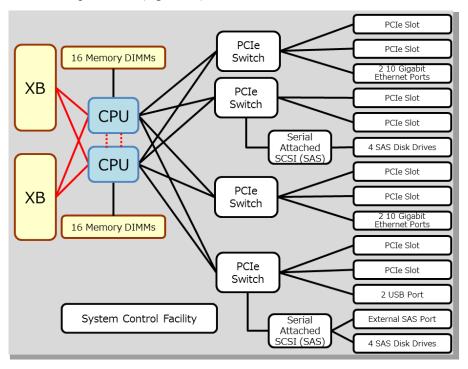

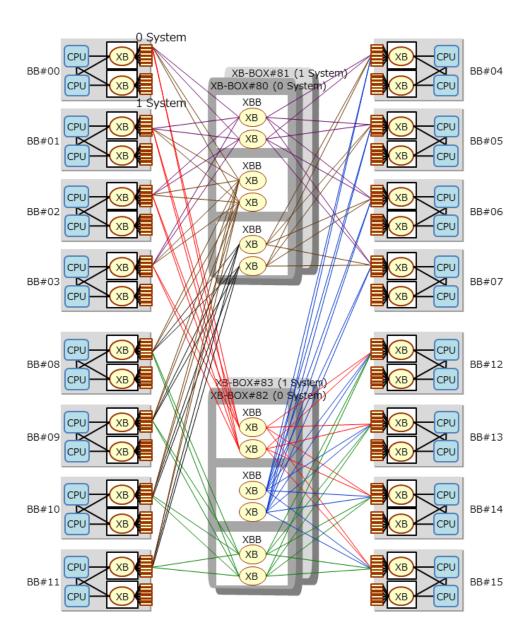

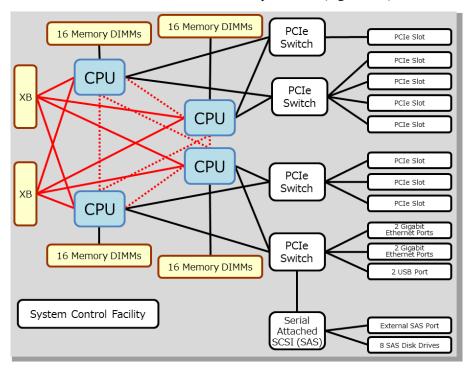

#### 7. Fujitsu M10-4S Interconnect Architecture

The Fujitsu M10-4S implements crossbar units in the server and crossbar boxes in order to connect multiple Fujitsu M10-4S chass is using the Building Block method. In each chass is, as in the Fujitsu M10-4, two physical system boards are implemented and function as a single logical system board. The Fujitsu M10-4 supports up to either four SPARC64 X+ processors or four SPARC64 X processors; and as with the Fujitsu M10-1, the memory access, I/O, and system controllers are embedded in the CPU. Each controller connects to DIMMs and PCI Express switches, and all four SPARC64 X+ or SPARC64 X processors are interconnected. To increase I/O bus bandwidth and protect against processor (Figure 4-10).

Figure 4-10. Fujitsu M10-4S Interconnect Architecture

The Fujitsu M10-4S, adopting the Building Block method, implements crossbar units to connect the system buses between Fujitsu M10-4S chassis. The system buses support low-latency and high-throughput data transfers.

To improve performance, the physical addressing of memory in the Building Block configuration is evenly spread out across the system controllers of all Fujitsu M10-4S chassis.

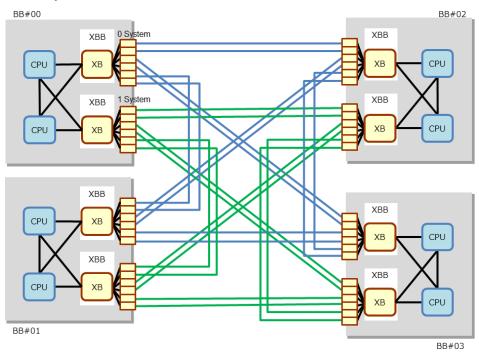

The SPARC64 X+ or SPARC64 X processor has a direct connection to the crossbar unit,

minimizing the latency of data transfers over multiple Fujitsu M10-4S chassis. You can use point-to-point connection to directly connect the built-in crossbar units of up to 4 Fujitsu M10-4S chassis and expand to up to 16 CPU chips (Figure 4-11). With system configurations scalable to up to 16 Fujitsu M10-4S chassis, each chassis is connected to all other chassis via crossbar boxes (Figure 4-12). The system interconnect used in the Fujitsu M10-4S delivers as much as 6,553 GB/second of peak bandwidth, offering 9 times more system throughput than Fujitsu's previous generation of high-end servers.

The Fujitsu M10-4S Building Blocks with mounted SPARC64 X processors can be connected to both the Fujitsu M10-4S Building Blocks with SPARC64 X processors and the Fujitsu M10-4S Building Blocks with SPARC64 X+ processors.

This ensures that the system can be upgraded to a higher-performance system without wasting existing investment in the Fujitsu M10-4S Building Blocks with SPARC64X processors.

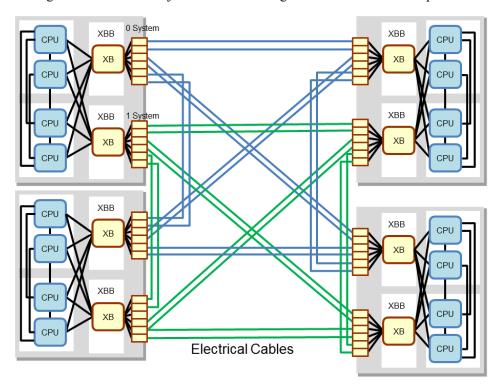

Figure 4-11. System Configuration Directly Connecting Servers (Fujitsu M10-4S 4BB)

Note: This figure shows only the connection between the BB (0 System) ports and XB-BOX (0 System). The BB (1 System) ports and XB-BOX (1 System) are also connected at the same time.

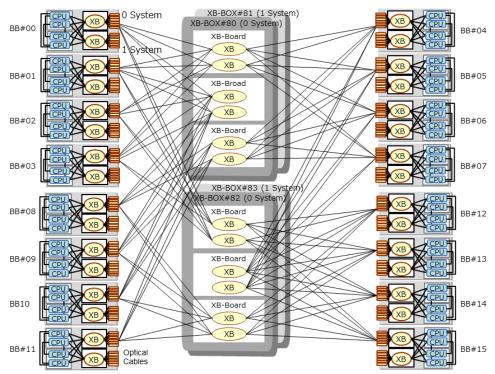

Figure 4-12. System Configuration of Connections via Crossbar Boxes (Fujitsu M10-4S 16BB)

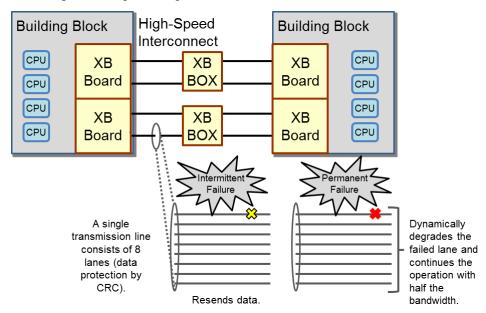

#### 8. System Interconnect Reliability Features

The built-in redundancy and reliability features of the Fujitsu SPARC M12 and Fujitsu M10 system interconnect enhance the stability of these servers. The interconnect is protected against loss or corruption of both transaction addresses and data by ECC or CRC protection on all system buses. When a single-bit data error is detected in a CPU, memory access controller, or I/O controller, hardware corrects the data and proceeds with the transfer. Also, when a multi-bit data error is detected by CRC on a bus that is connected via Fujitsu high-speed interconnect technology (all crossbar-crossbar, crossbar-processor, and processor-processor buses), the hardware automatically resends the data. If the error cannot be recovered by resending the data, the specific lane is degraded. In the rare event of a hardware failure within the system interconnect, the system uses the surviving bus route on restart, isolating the faulty lane and facilitating the resumption of operation.

Figure 4-13. System Interconnect Reliability Features

# Memory

The memory subsystem in the Fujitsu SPARC M12 or Fujitsu M10 increases system scalability and throughput. In a 16 Building Block configuration, the Fujitsu SPARC M12 accommodates up to 3 TB (24 memory slots per processor) or 2 TB (16 memory slots per processor) of memory, and the Fujitsu M10 accommodates up to 64 TB of memory. The Fujitsu SPARC M12 supports DDR4 DIMMs and the Fujitsu M10 supports DDR3 DIMMs, with up to 4-way memory interleaving in both the Fujitsu SPARC M12 and Fujitsu M10 to enhance system performance. The available DIMM capacities include 8 GB, 16 GB, 32 GB, and 64 GB. Further details about the memory subsystem are described in Table 4-1 and Table 4-2.

Table 4-1. Fujitsu SPARC M12 Memory Subsystem Specifications

|                                  | Fujitsu SPARC<br>M12-1 | Fujitsu SPARC<br>M12-2                                                           | Fujitsu SPARC<br>M12-2S<br>(1BB)                                                 | Fujitsu SPARC<br>M12-2S (16BB)                                      |

|----------------------------------|------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------|

|                                  |                        | DDR4-24                                                                          | 00/1866 (*1)                                                                     |                                                                     |

| Maximum Memory<br>Capacity       | 1 TB                   | 3 TB<br>(24 memory<br>slots/processor)<br>2 TB<br>(16 memory<br>slots/processor) | 3 TB<br>(24 memory<br>slots/processor)<br>2 TB<br>(16 memory<br>slots/processor) | 48 TB (24 memory slots/processor) 32 TB (16 memory slots/processor) |

| DIMM Slots, Maximum              | 16                     | 48<br>(24 memory<br>slots/processor)<br>32<br>(16 memory<br>slots/processor)     | 48<br>(24 memory<br>slots/processor)<br>32<br>(16 memory<br>slots/processor)     | 768 (24 memory slots/processor) 512 (16 memory slots/processor)     |

| Unit of Memory Interleave        | 4 or<br>8 DIMMs        | 8 DIMMs                                                                          | 8 DIMMs                                                                          | 8 DIMMs                                                             |

| Maximum Number of<br>Interleaves | 4                      | 4                                                                                | 4                                                                                | 64                                                                  |

<sup>\*1 24</sup> memory slots per processor, 24 DIMMs mounted

Table 4-2. Fujitsu M10 Memory Subsystem Specifications

|                           | Fujitsu M10-1   | Fujitsu M10-4 | Fujitsu<br>M10-4S<br>(1BB) | Fujitsu<br>M10-4S<br>(16BB) |

|---------------------------|-----------------|---------------|----------------------------|-----------------------------|

|                           | DDR3-1600/1333  |               |                            |                             |

| Maximum Memory Capacity   | 1 TB            | 4 TB          | 4 TB                       | 64 TB                       |

| DIMM Slots, Maximum       | 16              | 64            | 64                         | 1024                        |

| Unit of Memory Interleave | 4 or<br>8 DIMMs | 8 DIMMs       | 8 DIMMs                    | 8 DIMMs                     |

| Interleaves, Maximum      | 4               | 8             | 8                          | 128                         |

Beyond performance, the Fujitsu SPARC M12/Fujitsu M10 memory subsystem is built with reliability in mind. ECC protection is implemented for all data stored in main memory, and the following advanced features foster early diagnosis and fault isolation that preserve system integrity and raise application availability.

#### - Memory patrol

Memory patrol periodically scans memory for errors. This proactive function prevents the use of faulty areas of memory before they can cause system or application errors, thereby improving system reliability.

#### - Memory Extended ECC

The Memory Extended ECC function provides single-bit error correction, supporting continuous operation even when events caused by memory device failures like burst read errors occur. This feature is similar to IBM's Chipkill technology.

#### Memory Mirroring

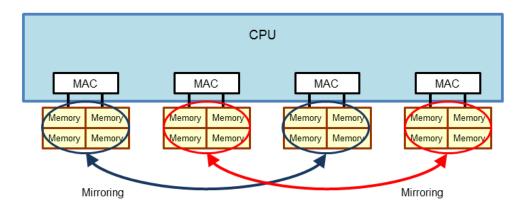

The Fujitsu SPARC M12 and Fujitsu M10 support memory mirroring capabilities. Memory mirroring is a high-availability feature appropriate when running applications with the most stringent availability requirements. When memory mirroring mode is enabled on the Fujitsu SPARC M12 or Fujitsu M10, the memory subsystem duplicates the data on write and compares the data on read to each side of the memory mirror. In the event that errors occur at the bus or DIMM level, normal data processing continues through the other memory bus and alternate DIMM set. In the Fujitsu SPARC M12 and Fujitsu M10, memory can be mirrored between memory modules, using the memory access controller (MAC) built into the SPARC64 XII, SPARC64 X+, and SPARC64 X processors (Figure 4-14).

Figure 4-14. Fujitsu SPARC M12 and Fujitsu M10 Memory Mirroring Architecture

#### System Clock

In the Fujitsu SPARC M12 and Fujitsu M10, the system clock is implemented independently for each CPU. Therefore, even after a system clock failure, the system can be restarted by degrading only the failed processor.

#### I/O Bus

The Fujitsu SPARC M12 and Fujitsu M10 use PCI Express buses to provide high-speed data transfer within the I/O subsystem. To provide optimal I/O performance for current and future PCI Express cards (such as Fibre Channel, InfiniBand, Gigabit Ethernet, and Flash PCI Express cards), the Fujitsu SPARC M12 and Fujitsu M10 implement the PCI Express 3.0 protocol in each processor. The peak data transfer rate of PCI Express 3.0 reaches 8 GB/s of throughput.

#### 1. I/O Subsystem Architecture

PCI Express switches provide the connections between the SPARC64 XII, SPARC64 X+, or SPARC64 X processor and PCI Express slots, onboard devices, and internal drives. The PCI Express bus can also be extended with PCI Expansion Units to provide a significant increase in PCI Express slots. The Fujitsu SPARC M12 and Fujitsu M10 I/O architecture has been designed to provide the scalability and performance (latest PCI Express 3.0 high throughput) required for server consolidation and virtualization.

To facilitate hot plugging of PCI Express cards, the Fujitsu SPARC M12-2, Fujitsu SPARC M12-2S, Fujitsu M10-4 and Fujitsu M10-4S and the PCI Express cassettes. PCI Express cards that support PCI hot plug can be mounted in PCI Express cassettes and then inserted into onboard or PCI Express ion Unit PCI Express slots of a running server.

#### 2. Fujitsu SPARC M12-1 I/O Subsystem

A depiction of the I/O subsystem of the Fujitsu SPARC M12-1 is shown in Figure 4-15. The figure shows two PCI Express switches mounted on the physical system board of the Fujitsu SPARC M12-1. These switches connect to all I/O components and the I/O controller in the processor. The I/O subsystem provides three PCI Express slots, one external SAS port, and two USB ports (Front: USB 2.0, Rear: USB 3.0). The external SAS port can be used to connect an SAS tape or storage device, and the USB ports to connect any supported DVD devices. You can increase these slots by connecting a PCI Expansion Unit.

Figure 4-15. Fujitsu SPARC M12-1 I/O Subsystem Architecture

#### 3. Fujitsu SPARC M12-2 I/O Subsystem

Four PCI Express switches are mounted on the physical system board of the Fujitsu SPARC M12-2. These switches connect all I/O components to the I/O controller in the processor. The PCI Express switches and the I/O controller in the CPU are connected one-to-one or one-to-two, depending on the number of CPU chips mounted. The I/O subsystem enables redundant configuration with two internal SAS controllers and two 10 GbE controllers. The I/O subsystem provides 11 PCI Express slots, 1 external SAS port, and 2 USB ports (Front: USB 2.0, Rear: USB 3.0). The external SAS port can be used to connect an SAS tape or storage device, and the USB ports to connect any supported DVD devices. You can increase these slots by connecting a PCI Expansion Unit.

Figure 4-16. Fujitsu SPARC M12-2 I/O Subsystem Architecture

#### 4. Fujitsu SPARC M12-2S I/O Subsystem

Four PCI Express switches are mounted on the physical system board of the Fujitsu SPARC M12-2S. These switches connect all I/O components to the I/O controller in the processor. The PCI Express switches and the I/O controller in the CPU are connected one-to-one or one-to-two, depending on the number of CPU chips mounted. The I/O subsystem enables redundant configuration with two internal SAS controllers and two 10 GbE controllers. The I/O subsystem provides eight PCI Express slots, one external SAS port, and two USB ports (Front: USB 2.0, Rear: USB 3.0). The external SAS port can be used to connect an SAS tape or storage device, and the USB ports to connect any supported DVD devices. You can increase these slots by connecting a PCI Expansion Unit.

Figure 4-17. Fujitsu SPARC M12-2S I/O Subsystem Architecture

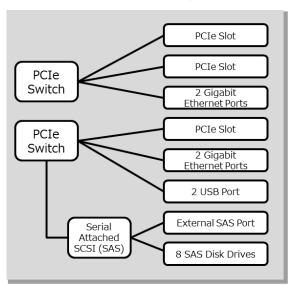

#### 5. Fujitsu M10-1 I/O Subsystem

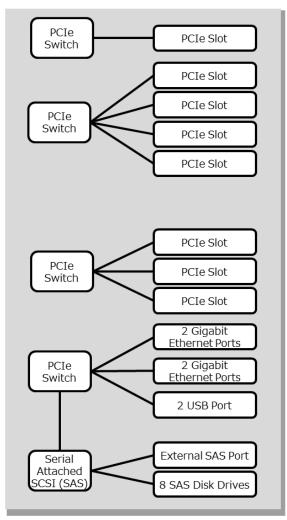

Two PCI Express switches are mounted on the physical system board of the Fujitsu M10-1. These switches connect all I/O components to the I/O controller in the SPARC64 X+ or SPARC64 X processor. The I/O subsystem provides three PCI Express slots, one external SAS port, and two USB 2.0 ports. The external SAS port can be used to connect an SAS tape or storage device, and the USB 2.0 ports to connect any supported DVD devices. You can increase these slots by connecting a PCI Expansion Unit.

Figure 4-18. Fujitsu M10-1 I/O Subsystem Architecture

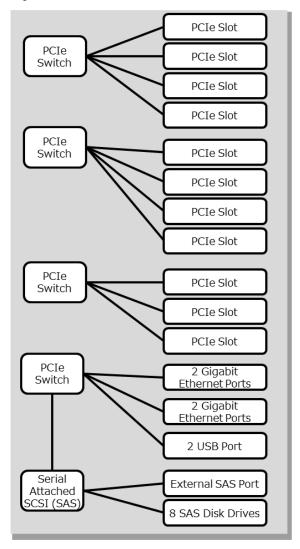

#### 6. Fujitsu M10-4 I/O Subsystem

Four PCI Express switches are mounted on the physical system board of the Fujitsu M10-4. These switches connect all I/O components to the I/O controller in the SPARC64 X+ or SPARC64 X processor. The PCI Express switches and the I/O controller in the CPU are connected one-to-one or one-to-two, depending on the number of CPU chips mounted. The I/O subsystem provides 11 PCI Express slots, 1 external SAS port, and 2 USB 2.0 ports. The external SAS port can be used to connect an SAS tape or storage device, and the USB 2.0 ports to connect any supported DVD devices. You can increase these slots by connecting a PCI Expansion Unit.

Figure 4-19. Fujitsu M10-4 I/O Subsystem Architecture

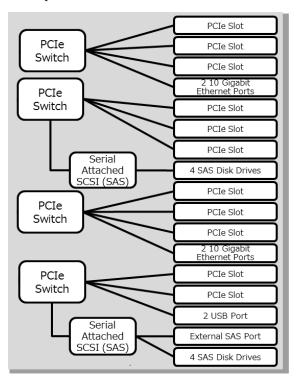

#### 7. Fujitsu M10-4S I/O Subsystem

Four PCI Express switches are mounted on the physical system board of the Fujitsu M10-4S. These switches connect all I/O components to the I/O controller in the SPARC64 X+ or SPARC64 X processor. The PCI Express switches and the I/O controller in the CPU are connected one-to-one or one-to-two, depending on the number of CPU chips mounted in each Fujitsu M10-4S chass is. The I/O subsystem provides eight PCI Express slots, one external SAS port, and two USB 2.0 ports per Fujitsu M10-4S chass is. The external SAS port can be used to connect an SAS tape or storage device, and the USB 2.0 ports to connect any supported DVD devices. You can increase these slots by connecting a PCI Expansion Unit.

Figure 4-20. Fujitsu M10-4S I/O Subsystem Architecture

#### 8. Internal Drives and Peripherals

The Fujitsu SPARC M12 and Fujitsu M10 support eight hot-swappable internal Serial Attached SCSI (SAS) 2.5-inch hard disk drives and 2.5-inch SSDs. Fujitsu SPARC M12 on-board SAS controllers support RAID 0, RAID 1, RAID 1E, and RAID 10 volumes and hot-swap drives. Fujitsu M10 on-board SAS controller supports RAID 0, RAID 1, and RAID 1E volumes and hot-swap drives. The Fujitsu SPARC M12 and Fujitsu M10 also provide one external SAS port, which can be connected to a SAS tape or storage device. The SAS port offers 4 lanes, supporting up to 24 Gbps total bandwidth. Also, the Fujitsu SPARC M12 supports one USB 3.0 port and one USB 2.0 port, and the Fujitsu M10 supports two USB 2.0 ports, which may be used to connect a supported DVD drive.

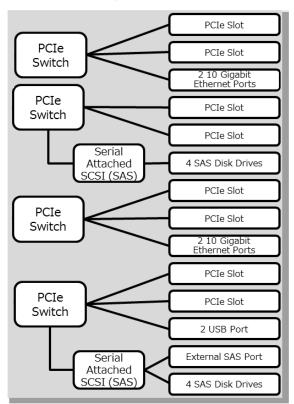

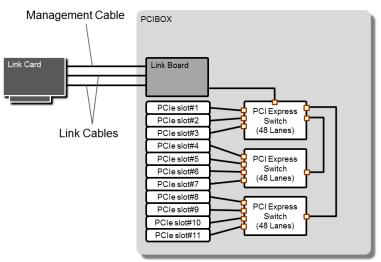

#### 9. PCI Expansion Unit

The Fujitsu SPARC M12 and Fujitsu M10 support the attachment of optional PCI Expansion Units to provide additional I/O connectivity. The PCI Expansion Unit is a 2U rack-mountable device that accommodates up to 11 PCI Express slots. By using PCI Express cassettes, the PCI Expansion Unit supports the hot-swapping of PCI Express cards.

A link card mounted in a PCI Express slot in the server provides connectivity to the PCI Expansion Unit and supports management control via sideband signals. The link card is a low-profile card and includes an 8-lane PCI Express bus with 8 GB/s bandwidth. The PCI Expansion Unit architecture of the Fujitsu SPARC M12 and Fujitsu M10 provides high-throughput I/O performance, supporting maximum data rates for various current and future PCI Express cards (such as Fibre Channel, InfiniBand, Gigabit Ethemet, and Flash PCI Express cards).

Figure 4-21. PCI Expansion Unit Architecture

A PCI Expansion Unit connects from the link board in the PCI Expansion Unit to the link card mounted in a PCI Express slot in the server through a cable. Cable options include a copper cable kit and a fibre cable kit. The Fujitsu SPARC M12 and Fujitsu M10 support the connection of multiple PCI expansion units as shown in Table 4-3 and Table 4-4.

Table 4-3. Connectable PCI Expansion Units on Fujitsu SPARC M12

|                                   | CPU configuration | OS Version             | Connectable PCI Expansion Units (Maximum) |

|-----------------------------------|-------------------|------------------------|-------------------------------------------|

| Fujitsu SPARC M12-1               | 1 (2011)          | Oracle Solaris 11 (*1) | 3                                         |

|                                   | 1 CPU             | Oracle Solaris 10 (*2) | 2                                         |

|                                   | 1 CDII            | Oracle Solaris 11 (*1) | 4 (*3) or 3 (*4)                          |

| Fujitsu SPARC M12-2               | 1 CPU             | Oracle Solaris 10 (*2) | 2                                         |

|                                   | 2 CDII            | Oracle Solaris 11 (*1) | 8 (*3) or 6 (*4)                          |

|                                   | 2 CPU             | Oracle Solaris 10 (*2) | 6                                         |

|                                   | 1 CDII            | Oracle Solaris 11 (*1) | 4 (*3) or 3 (*4)                          |

| Fujitsu SPARC M12-2S (per Server) | 1 CPU             | Oracle Solaris 10 (*2) | 2                                         |

|                                   | 2 CDII            | Oracle Solaris 11 (*1) | 8 (*3) or 5 (*4)                          |

|                                   | 2 CPU             | Oracle Solaris 10 (*2) | 5                                         |

<sup>\*1</sup> Oracle Solaris 11: OS versions on the control domain, root domain, and I/O domain are all Oracle Solaris 11.

Table 4-4. Connectable PCI Expansion Units on Fujitsu M10

|                | CPU configuration | Connectable PCI Expansion Units<br>(Maximum) |

|----------------|-------------------|----------------------------------------------|

| Fujitsu M10-1  | 1 CPU             | 2                                            |

|                | 2 CPUs            | 3                                            |

| Fujitsu M10-4  | 4 CPUs            | 6                                            |

| Fujitsu M10-4S | 2 CPUs            | 3                                            |

| (per Server)   | 4 CPUs            | 5                                            |

<sup>\*2</sup> Oracle Solaris 10: OS versions on the control domain, root domain, and I/O domain are all Oracle Solaris 10 or a mixture of Oracle Solaris 11 and Oracle Solaris 10.

<sup>\*3</sup> For firmware version XCP 3040 or later

<sup>\*4</sup> For firmware version XCP 3030 or earlier

# Cooling

The Fujitsu SPARC M12-1 and Fujitsu M10-1 use fans for air cooling. The Fujitsu SPARC M12-2 and M12-2S and the Fujitsu M10-4 and M10-4S employ a technology that effectively cools the heat of the processor to increasingly boost its performance.

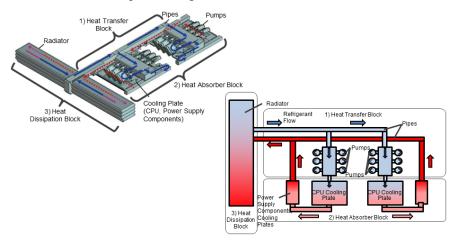

#### Liquid Loop Cooling (LLC)

The Fujitsu M10-4 and Fujitsu M10-4S employ Liquid Loop Cooling (LLC). This cooling method combines the advantages of liquid cooling technology (high cooling performance) with the advantages of air cooling technology (ease of installation and operation). LLC consists of the following three functional blocks:

- 1. Heat transfer block: Pipes and pumps

- 2. Heat absorber block: Cooling plates

- 3. Heat dissipation block: Radiator

Refrigerant is circulated in the LLC system by pumps in the heat transfer block. In the heat absorber block, the refrigerant absorbs heat dissipated from the cooling plate mounted to the CPU and power supply components. The refrigerant flows through the pipes of the heat transfer block, and is sent into the radiator where it is cooled by forced air from fans mounted in the front of the chassis. The refrigerant returns through the pipes and pumps back to the cooling plate.

By circulating the refrigerant entirely within the chassis, LLC enhances the ease of server installation and serviceability because there is no need to supply liquid from outside or perform maintenance on the liquid cooling mechanism.

Figure 4-22. Mechanism of Liquid Loop Cooling

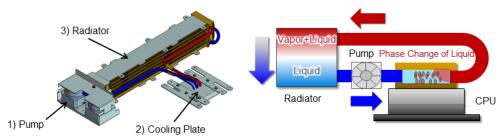

#### Vapor and Liquid Loop Cooling (VLLC)

The Fujitsu SPARC M12-2 and Fujitsu SPARC M12-2S employ Vapor and Liquid Loop Cooling (VLLC), a new cooling technology using evaporative cooling, instead of LLC.

Like LLC, VLLC consists of the following three functional blocks:

- 1. Heat transfer block: Pipes and pumps

- 2. Heat absorber block: Cooling plate

- 3. Heat dissipation block: Radiator

As with LLC, pumps in the heat transfer block circulate refrigerant in the VLLC system, and the radiator dissipates the heat absorbed by the cooling plate into the air.

VLLC uses evaporative cooling, which absorbs heat as the liquid changes to vapor, in addition to the LLC method of hybrid cooling with air and water cooling technologies.

VLLC achieves approximately two times better cooling performance than LLC, while keeping the following LLC features: maintenance-free, ease of server installation, and serviceability.

Figure 4-23. Mechanism of Vapor and Liquid Loop Cooling

### High-Efficiency Power Supplies

The Fujitsu SPARC M12 and Fujitsu M10 employ power supply units that are 80 PLUS (\*1) certified, indicating the high power conversion efficiency of computer power supply units. Specifically, they are 80 PLUS PLATINUM certified.

The power supply units of the Fujitsu SPARC M12-2 and M12-2S and the Fujitsu M10-4 and M10-4S realize high power conversion efficiency with the following technologies.

- Low-loss components: SiC diodes and Super Junction FETs

Traditional silicon-based power semiconductors in switching power supply circuits have been replaced with low-loss power semiconductors, such as SiC diodes and Super Junction FETs, to lower the power loss.

- High-efficiency circuits: Bridge-less rectifier and standby-less power feed circuits Bridge-less rectifier circuits, which control rectifier and later-stage PFC (Power Factor Correction) circuits in an integrated fashion, are adopted to achieve high conversion efficiency by reducing the number of stages of power conversion circuits. In addition, Fujitsu's unique standby-less power feed method, which feeds power solely from the main power supply, achieves high efficiency with fewer standby power supply circuits.

- Secondary-side low-loss wiring: Bus bar structure of wiring in the secondary-side output section

The printed-circuit boards previously used for connection between power supply units and secondary-side power components have been replaced with wiring in a copper bus bar structure that reduces direct-current resistance to lower the power loss.

URL: <a href="https://plugloadsolutions.com/80pluspowersupplies.aspx">https://plugloadsolutions.com/80pluspowersupplies.aspx</a>

<sup>\*1 80</sup> PLUS is a program for power-saving electrical equipment, promoted by the 80 PLUS® Program. It indicates that a power supply unit has an 80% or higher efficiency of power conversion from alternating current to direct current. The efficiency rises in the order shown in the rankings of STANDARD, BRONZE, SILVER, GOLD, PLATINUM, and TITANIUM.

# 5. System Management

# Reliability, Availability, and Serviceability

To reduce downtime without impacting the availability of key services, mechanisms that foster fault resilience and quick repair are required. A mechanism for rapid expansion must also be included. Specifically designed to support complex, network computing solutions and stringent high-availability requirements, the Fujitsu SPARC M12 and Fujitsu M10 include redundant and hot-swappable system components, diagnostic and error recovery features throughout the design, and built-in remote management features. The advanced architecture of these reliable servers delivers high levels of application availability and rapid recovery from many types of hardware faults, simplifying system operation and lowering costs for enterprises.

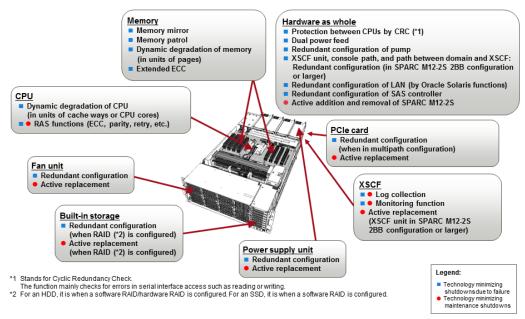

Figure 5-1. Reliability, Availability, and Serviceability of the Fujitsu SPARC M12

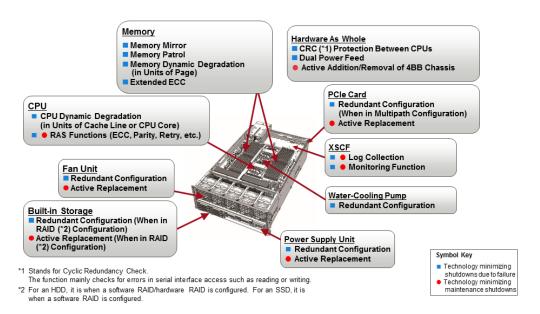

Figure 5-2. Reliability, Availability, and Serviceability of the Fujitsu M10

#### Redundant and Hot-Swappable Components

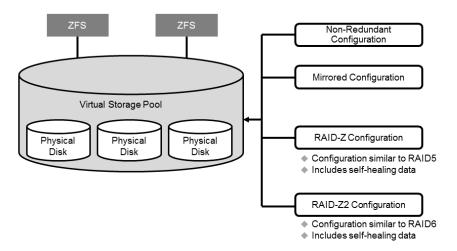

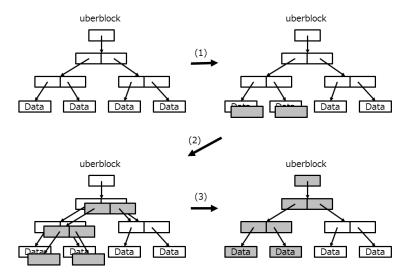

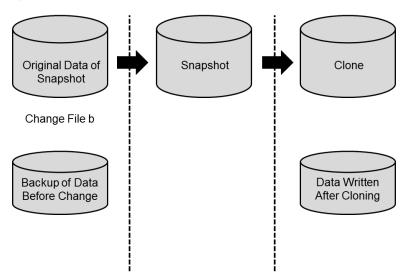

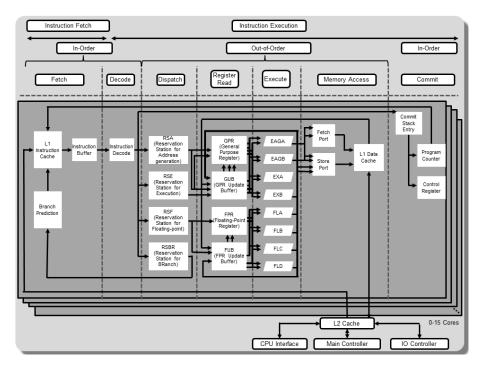

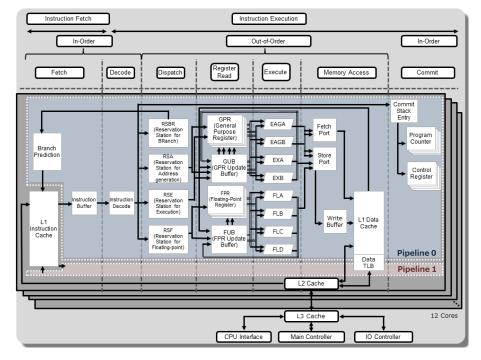

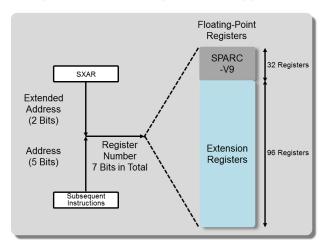

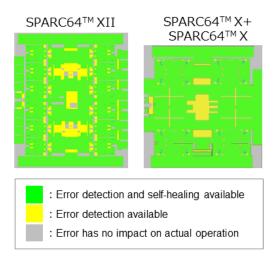

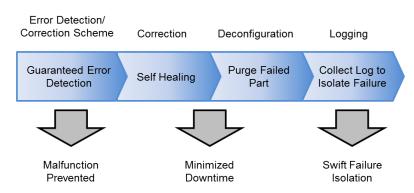

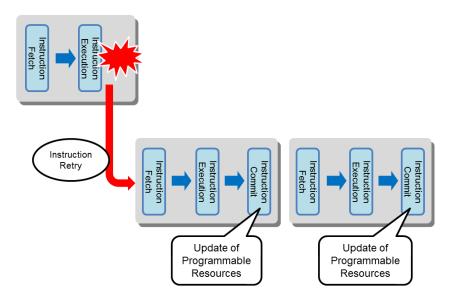

Today's IT organizations are challenged by the pace of non-stop business operations. This is forcing planned downtime windows to shrink and, in some cases, disappear entirely. To meet these demands, the Fujitsu SPARC M12 and Fujitsu M10 employ built-in redundant and hot-swappable hardware to help mitigate the disruptions caused by individual component failures or changes to system configurations. In fact, these systems are able to recover from hardware failures often with no impact to users or system functionality.